DIGITAL ELECTRONICS II-II NR21

## Number Systems

your roots to success...

#### Common Number Systems

N 1 💧 1 .

| System  | Base  | Symbols  | Used by humans? | Used in computers? |

|---------|-------|----------|-----------------|--------------------|

| Decimal | 10    | 0, 1, 9  | Yes             | No                 |

| Binary  | 2     | 0, 1     | No              | Yes                |

| Octal   | 8     | 0, 1, 7  | No              | No                 |

| Hexa-   | 16    | 0, 1, 9, | No              | No                 |

| decimal | V O D | A, B, F  | SHÉCESS         |                    |

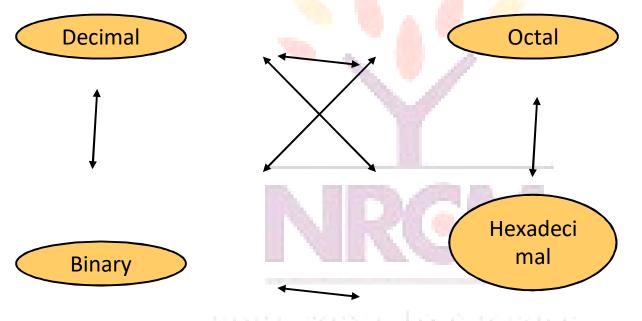

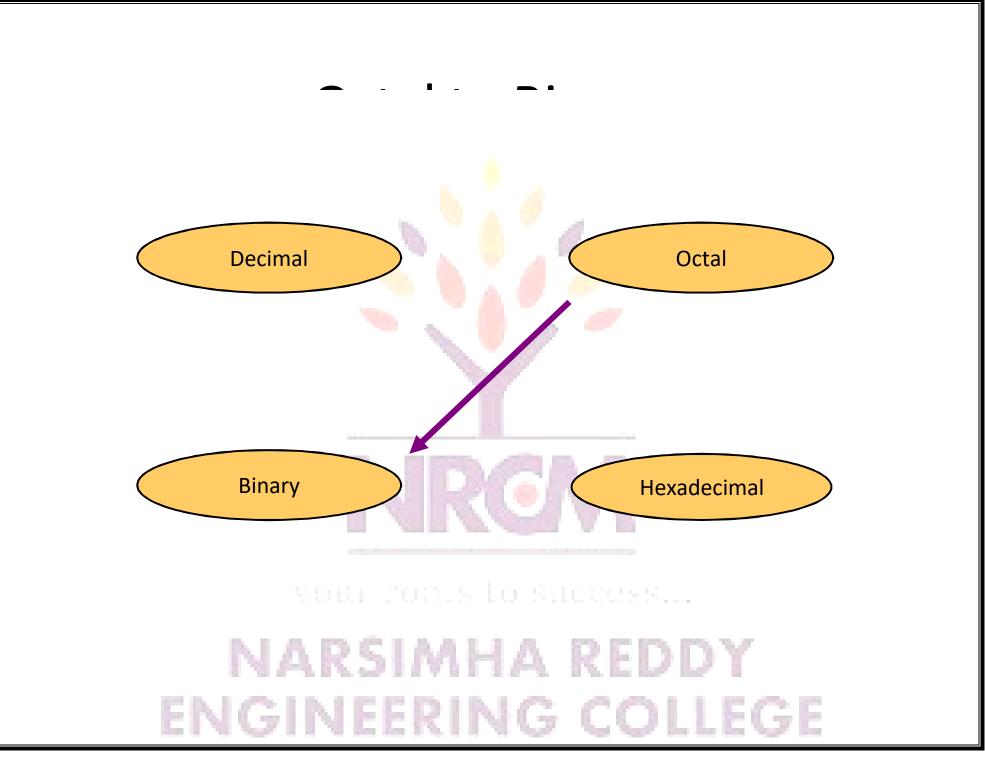

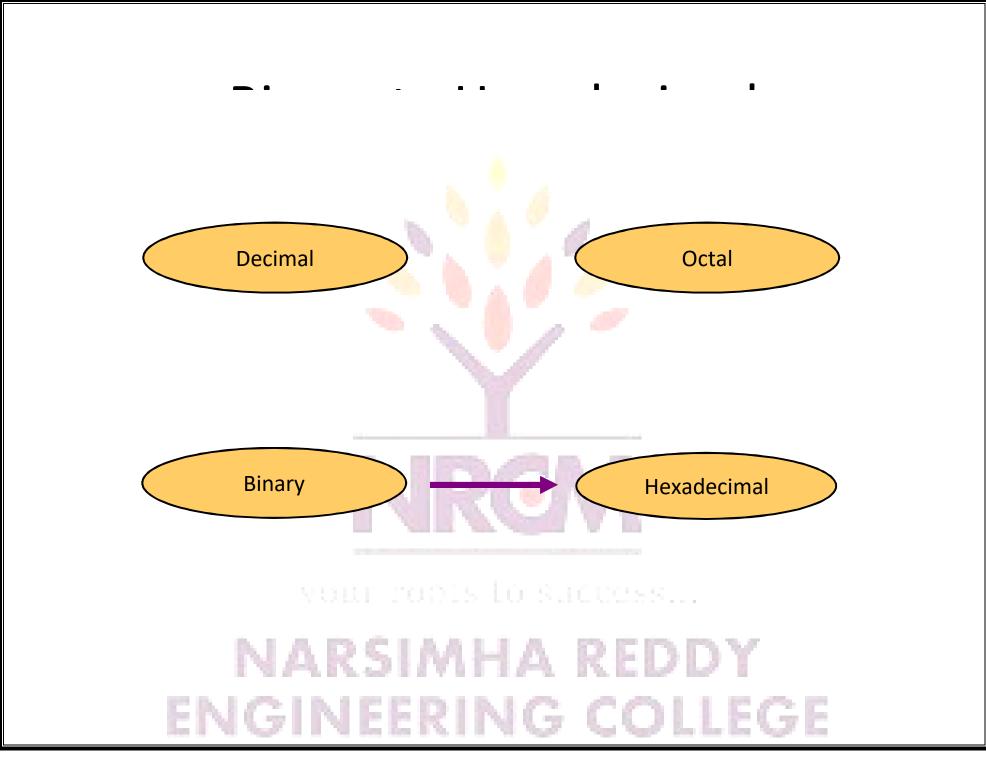

### **Conversion Among Bases**

The possibilities:

our robis lo suécess...

#### Quick Example 25<sub>10</sub> = 11001 = 31<sub>8</sub> = 19<sub>16</sub> HA REDDY ENGERING COLLEGE Base

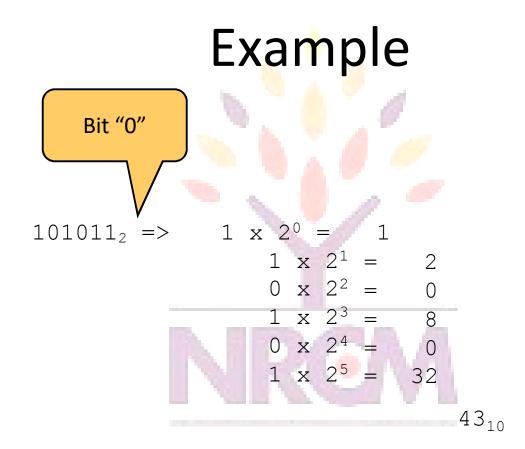

# Binary to Decimal

- Technique

- Multiply each bit by 2<sup>n</sup>, where n is the "weight" of the bit

- The weight is the position of the bit, starting from

0 on the right

- Add the results

your roots to success...

**DIGITAL ELECTRONICS II-II NR21**

your roots to success...

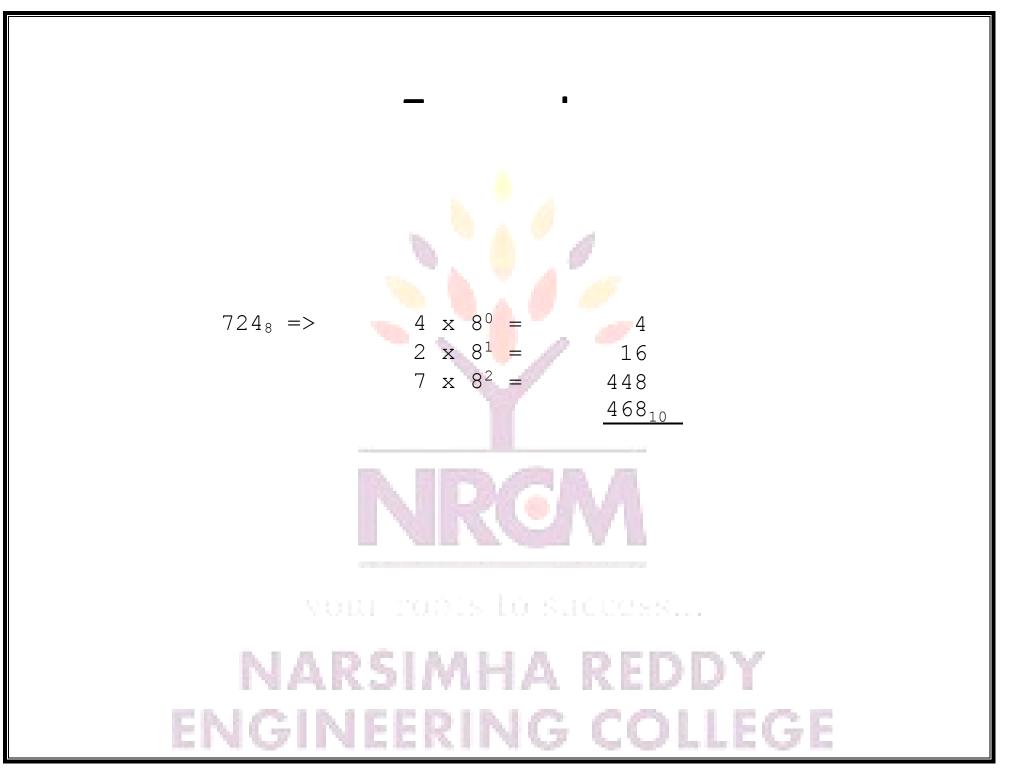

#### Octal to Decimal

- Technique

- Multiply each bit by 8', where n is the "weight" of the bit

- The weight is the position of the bit, starting from

0 on the right

- Add the results

your roots to success...

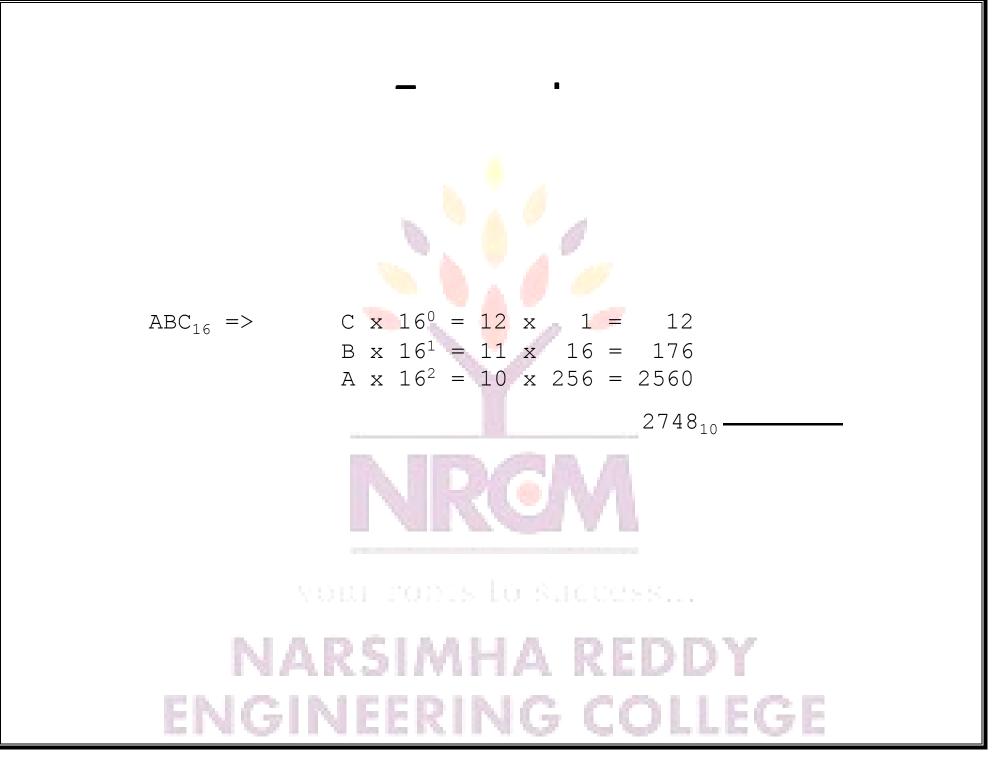

- Technique

- Multiply each bit by 16<sup>n</sup>, where n is the "weight" of the bit

- The weight is the position of the bit, starting from

0 on the right

- Add the results

your roots to success...

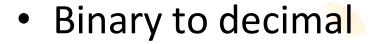

- Divide by two, keep track of the remainder

- First remainder is bit 0 (LSB, least-significant bit)

- Second remainder is bit 1

- Etc.

your roots to success...

$$125_{10} = ?_{2}$$

$$2 \frac{125}{31} \frac{1}{31} \frac{1}{$$

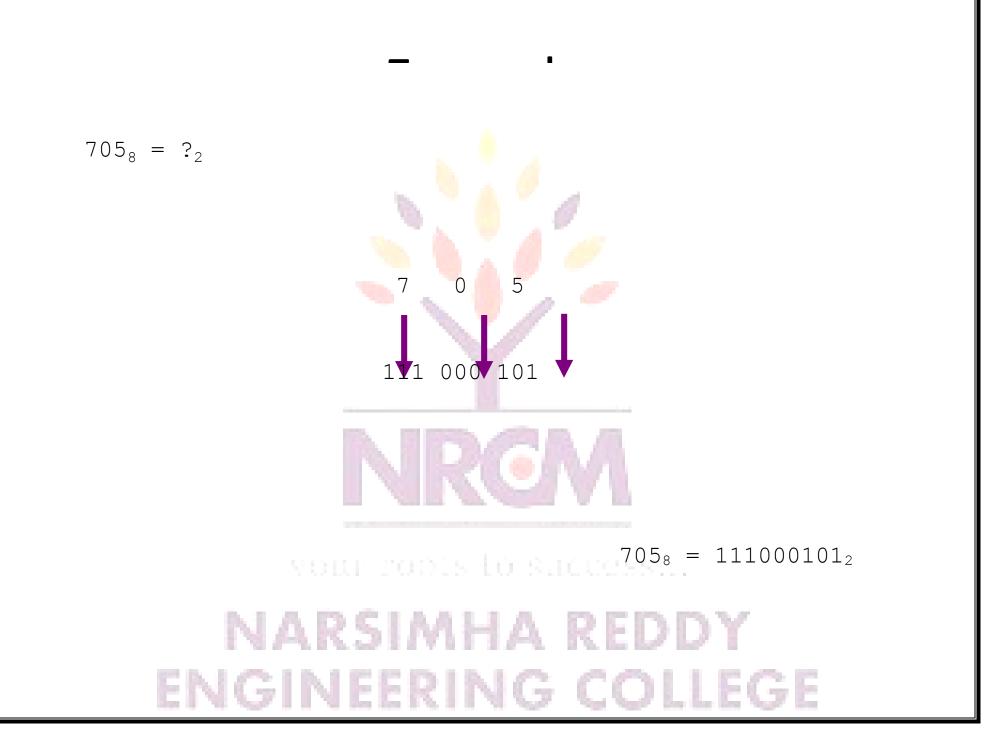

Convert each octal digit to a 3-bit equivalent binary representation

your roots to success....

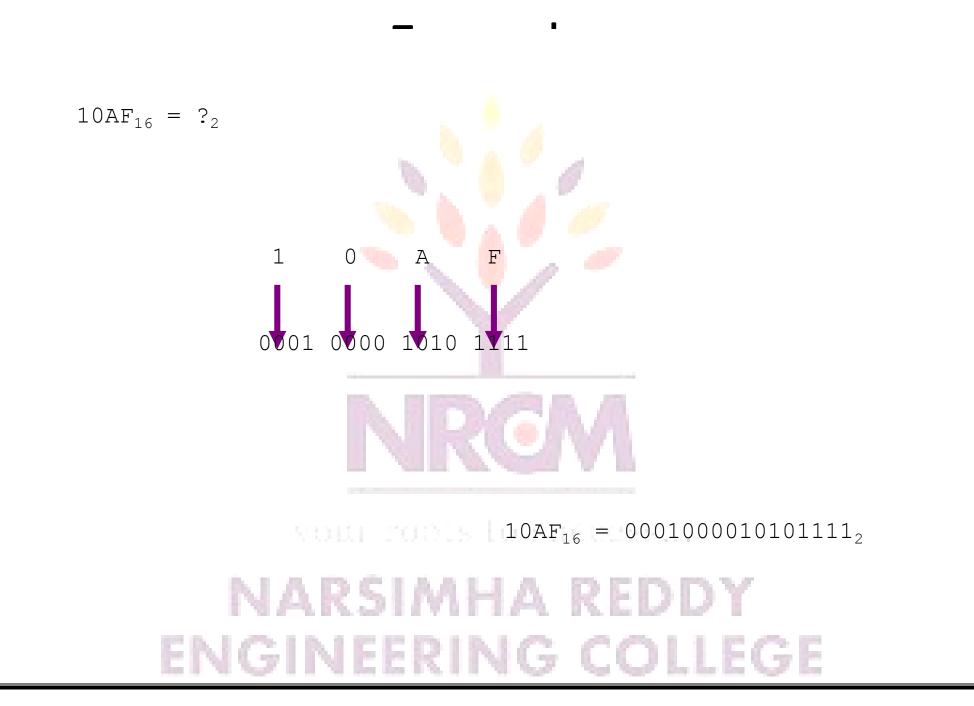

- Technique

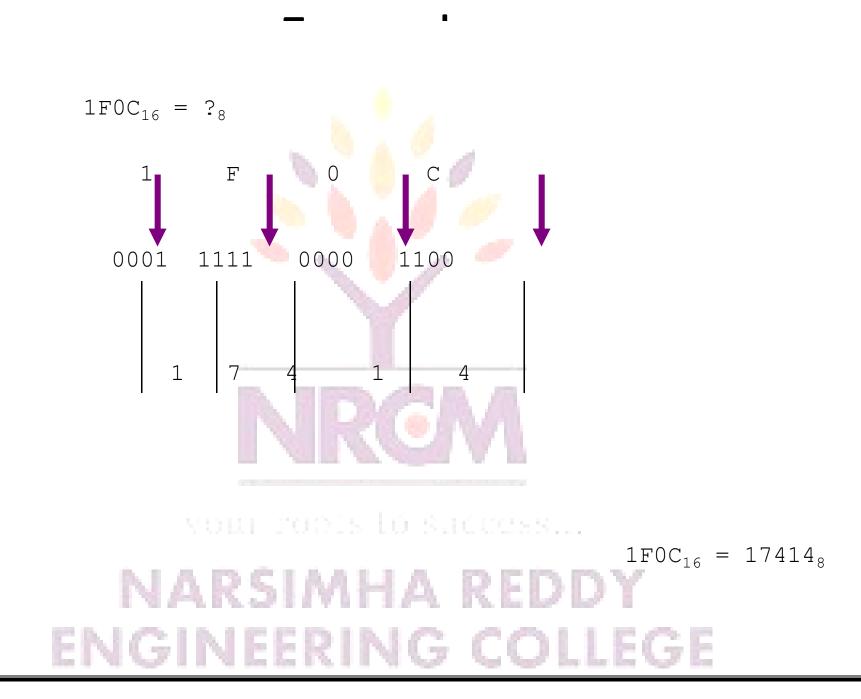

- Convert each hexadecimal digit to a 4-bit equivalent binary representation

your robis lo success...

- Technique

- Divide by 8

- Keep track of the remainder

your roots to success...

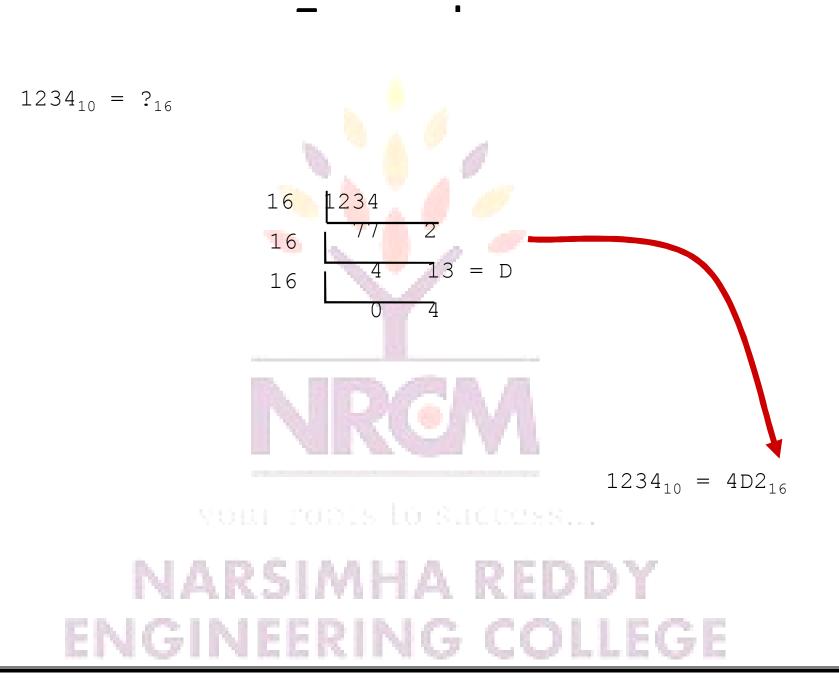

- Technique

- Divide by 16

- Keep track of the remainder

your roots to success...

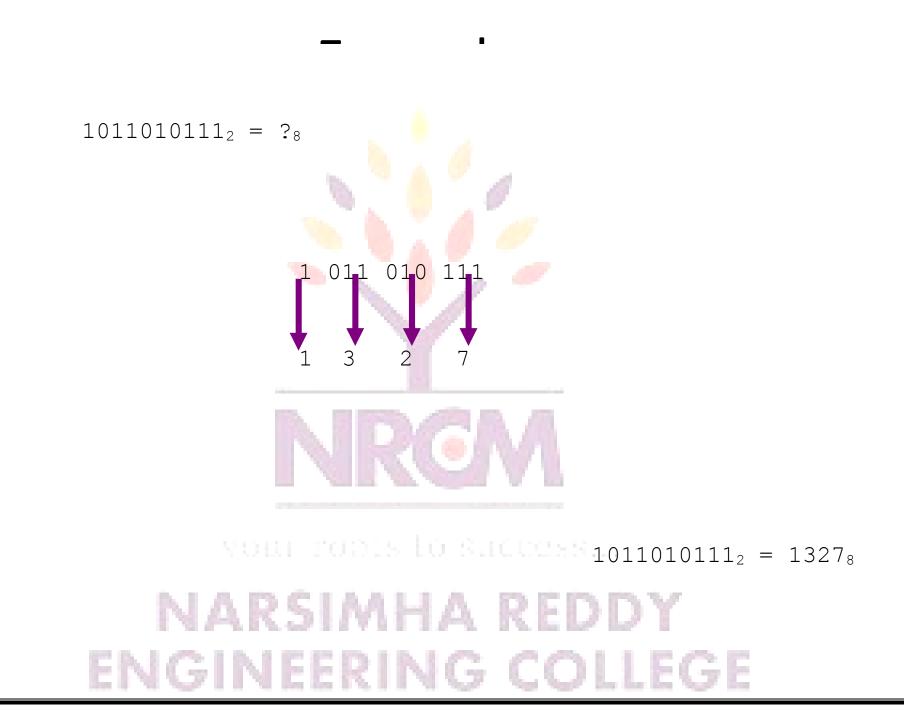

- Group bits in threes, starting on right

- Convert to octal digits

your robis lo success...

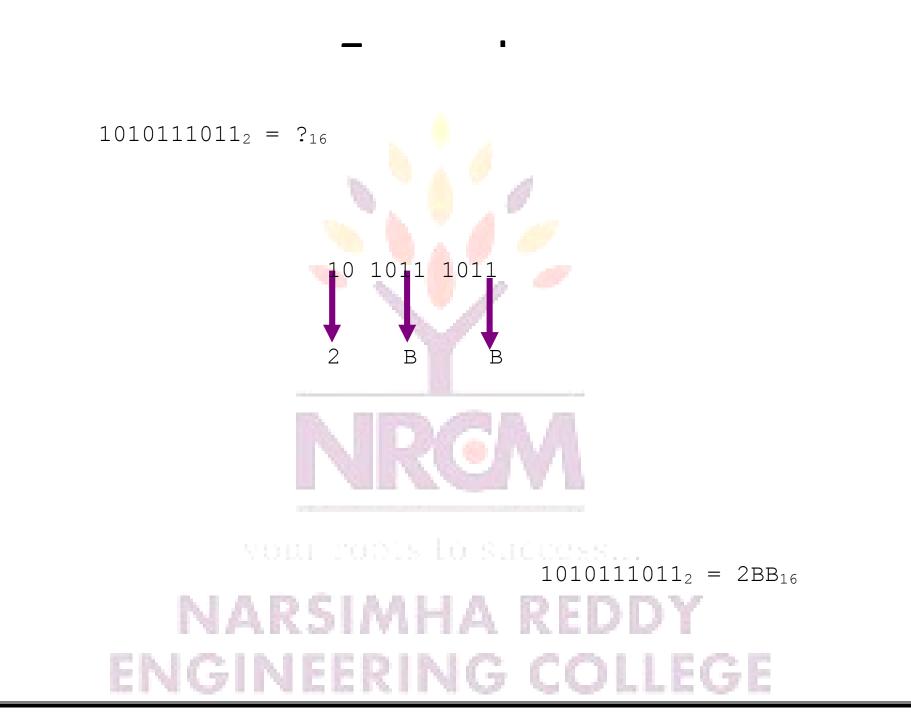

- Group bits in fours, starting on right

- Convert to hexadecimal digits

your robis lo success...

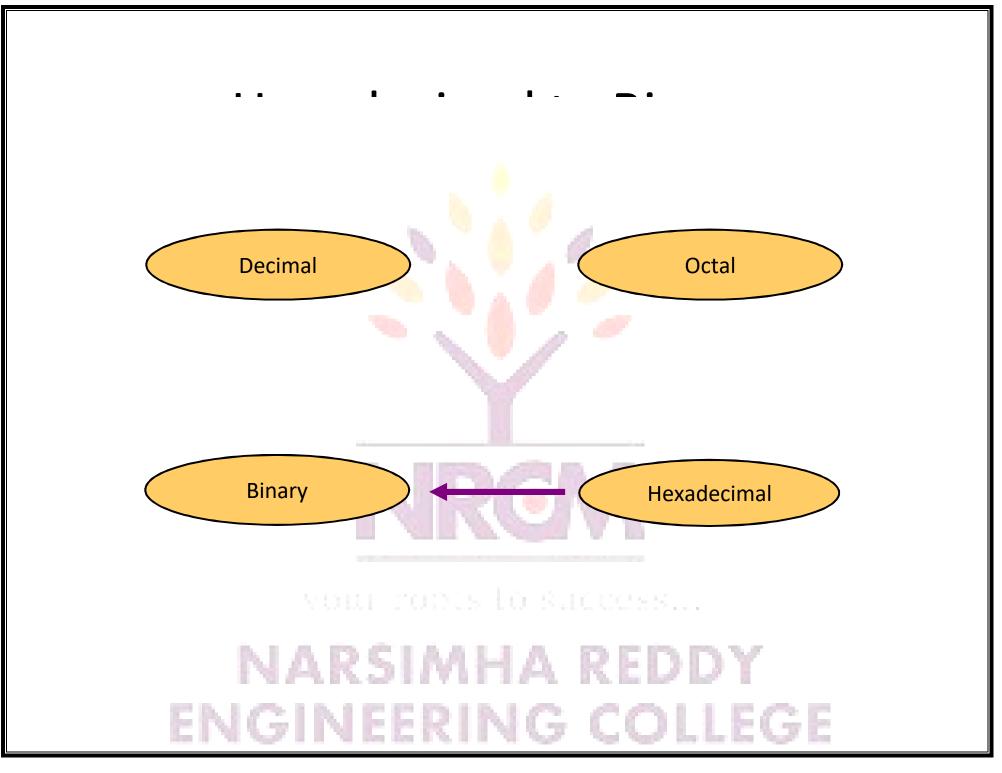

– Use binary as an intermediary

your roots to success...

#### Technique

– Use binary as an intermediary

your roots to successil.

Mr.M.SUNDER RAO ASSISTANT.PROFESSOR

Value

.00000000001

#### NARSIMHA REDDY ENGINEERING COLLEGE

|                | 10-9            | nano  | n | .000000001        |  |  |

|----------------|-----------------|-------|---|-------------------|--|--|

|                | 10-6            | micro | μ | .000001           |  |  |

|                | 10-3            | milli | m | .001              |  |  |

|                | 10 <sup>3</sup> | kilo  | k | 1000              |  |  |

|                | 10 <sup>6</sup> | mega  | М | 1000000           |  |  |

|                | 10 <sup>9</sup> | giga  | G | 1000000000        |  |  |

|                | 1012            | tera  | T | 10000000000000000 |  |  |

| NARSIMHA REDDY |                 |       |   |                   |  |  |

Symbol

p

Preface

pico

Power

10-12

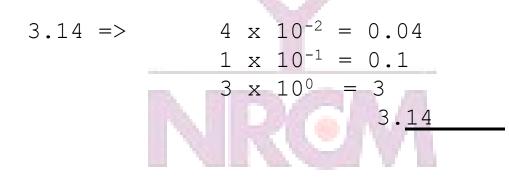

• Base 10

| -      |                 | _       | 1-     | 1          |

|--------|-----------------|---------|--------|------------|

|        |                 | . • .   |        |            |

| Base 2 | Power           | Preface | Symbol | Value      |

|        | 210             | kilo    | k      | 1024       |

|        | 220             | mega    | M      | 1048576    |

|        | 2 <sup>30</sup> | Giga    | G      | 1073741824 |

- What is the value of "k", "M", and "G"?

- In computing, particularly w.r.t. <u>memory</u>, the base-2 interpretation generally applies

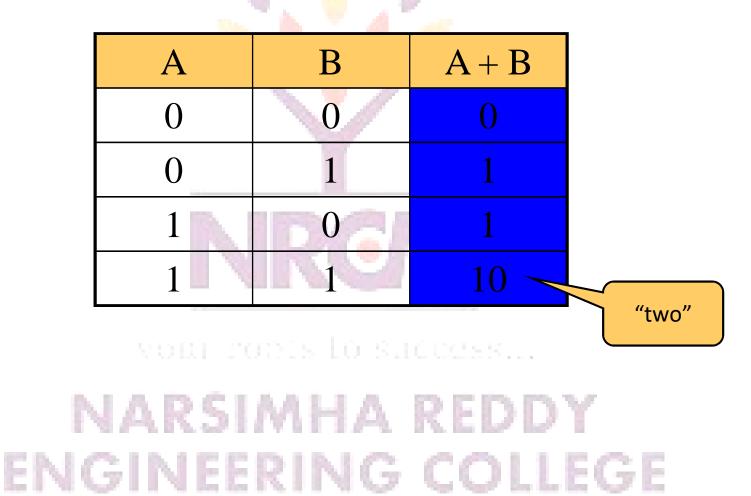

#### • Two 1-bit values

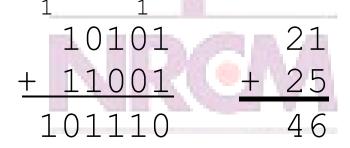

- Two *n*-bit values

- Add individual bits

- Propagate carries

- E.g.,

vour robis lo success...

NARSIMHA REDDY ENGINEERING COLLEGE

pp. 39

1110

1011

1110

1110

0000

10011010

NARSIMHA REDDY

ENGINEERING COLLEGE

1110

Х

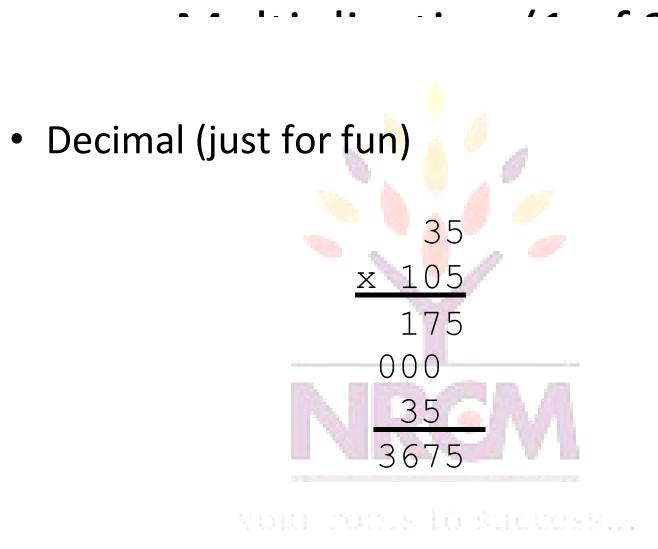

- Binary, two *n*-bit values

- As with decimal values

- E.g.,

Decimal to decimal (just for fun)

vour robis lo suécess...

# NARSIMHA REDDY

pp. 46-50

10.1011 =>

$\begin{array}{rcl} \Rightarrow & 1 \ x \ 2^{-4} \ = \ 0.0625 \\ & 1 \ x \ 2^{-3} \ = \ 0.125 \\ & 0 \ x \ 2^{-2} \ = \ 0.0 \\ & 1 \ x \ 2^{-1} \ = \ 0.5 \\ & 0 \ x \ 2^{0} \ = \ 0.0 \\ & 1 \ x \ 2^{1} \ = \ 2.0 \end{array}$

VORE FORES LO SHEURSSII.

2.6875

#### NARSIMHA REDDY ENGINEERING COLLEGE

рр. 46-50

p. 50

# **Boolean Algebra**

your roots to success...

## Introduction

- 1854: Logical algebra was published by George Boole → known today as "Boolean Algebra"

- It's a convenient way and systematic way of expressing and analyzing the operation of logic circuits.

- 1938: Claude Shannon was the first to apply Boole's work to the analysis and design of logic circuits.

#### **Boolean Operations & Expressions**

- Variable a symbol used to represent a logical quantity.

- Complement the inverse of a variable and is indicated by a bar over the variable.

- Literal a variable or the complement of a variable.

your roots to success...

## Laws & Rules of Boolean Algebra

- The basic laws of Boolean algebra:

- The commutative laws

- The **associative** laws

- The **distributive** laws

your roots to success...

#### **Commutative Laws**

The commutative law of addition for two variables is written as: A+B = B+A

$$A = A + B = A + B = A + B + A$$

• The *commutative law of multiplication* for two variables is written as: *AB* = *BA*

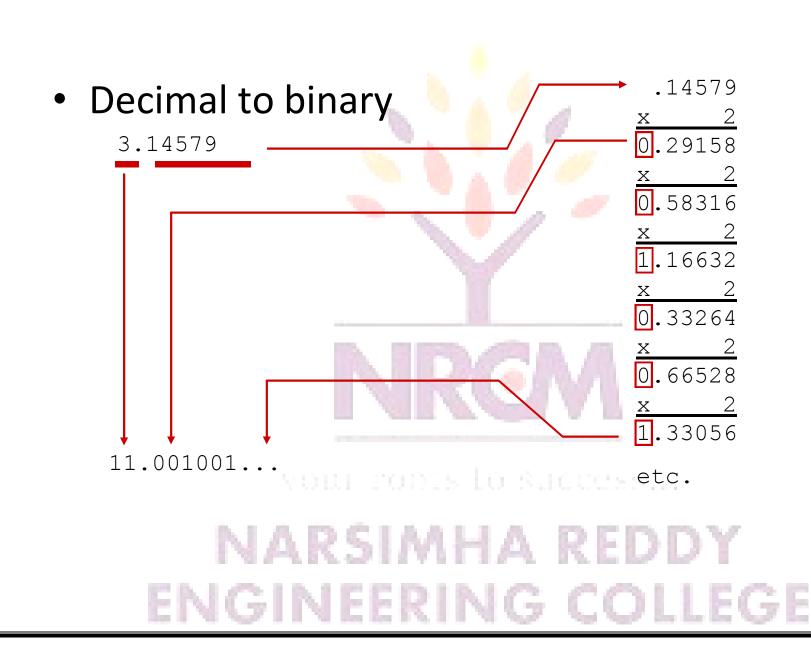

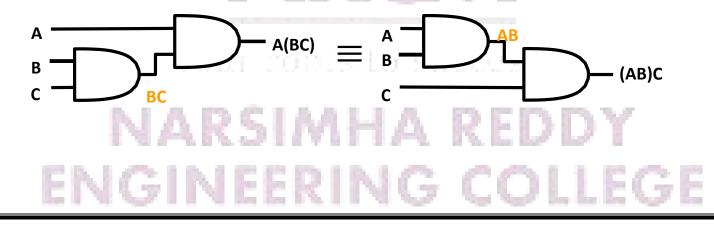

The associative law of addition for 3 variables is written as: A+(B+C) = (A+B)+C

The associative law of multiplication for 3 variables is written as: A(BC) = (AB)C

• The *distributive law* is written for 3 variables as follows: A(B+C) = AB + AC

$7.A \bullet A = A$ 1.A + 0 = A $8.A \bullet \overline{A} = 0$ 2.A + 1 = 1 $9.\overline{\overline{A}} = A$  $3.A \bullet 0 = 0$  $4.A \bullet 1 = A$ 10.A + AB = A5.A + A = A $11.A + \overline{A}B = A + B$  $6.A + \overline{A} = 1$ 12.(A+B)(A+C) = A + BCNARSIMHA REDDY ENGINEERING COLLEGE

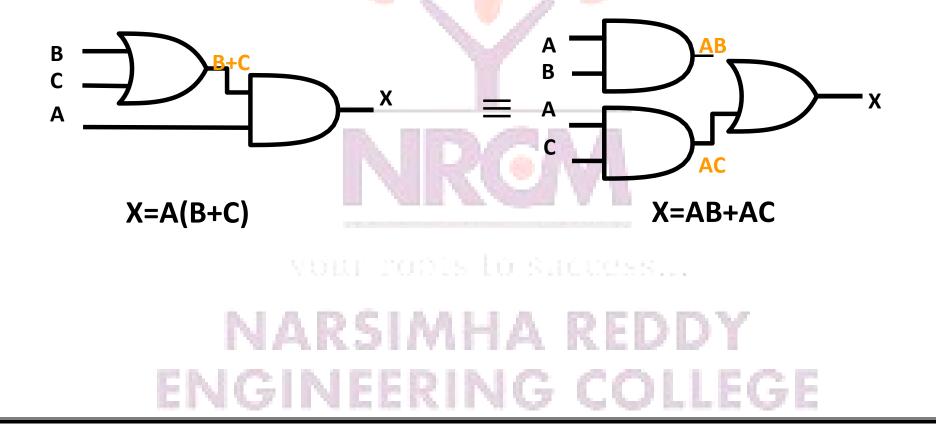

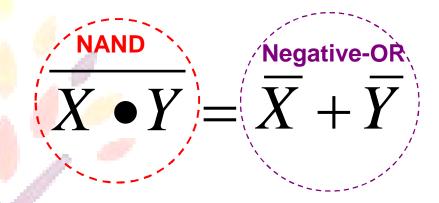

- DeMorgan's theorems provide mathematical verification of:

- the equivalency of the NAND and negative-OR gates

- the equivalency of the NOR and negative-AND gates.

your roots to success...

The complement of two or more ANDed variables is equivalent to the OR of the complements of the individual variables.

$X + Y \models X \bullet Y$

Negative-AND

The complement of two or more ORed variables is equivalent to the AND of the complements of the individual variables.

Apply DeMorgan's theorems to the expressions:

(A+B+C)D

$\overline{ABC + DEF}$

$A\overline{B} + \overline{C}D + EF$

A + BC + D(E + F)NARSIMHA REDDY ENGINEERING COLLEGE

- Boolean algebra provides a concise way to express the operation of a logic circuit formed by a combination of logic gates

- so that the output can be determined for various combinations of input values.

your robis lo success...

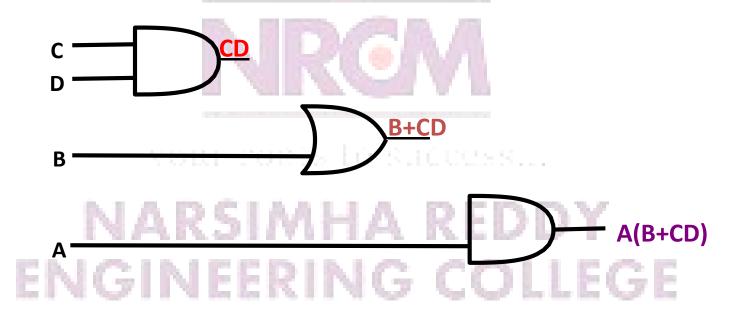

Boolean Expression for a Logic Circuit

To derive the Boolean expression for a given logic circuit, begin at the left-most inputs and work toward the final output, writing the expression for each gate.

- Once the Boolean expression for a given logic circuit has been determined, a truth table that shows the output for all possible values of the input variables can be developed.

- Let's take the previous circuit as the example:

A(B+CD)

- There are four variables, hence 16 (2<sup>4</sup>) combinations of values are possible.

ENGINEERING COLLEGE

- Evaluating the expression

- To evaluate the expression A(B+CD), first find the values of the variables that make the expression equal to 1 (using the rules for Boolean add & mult).

- In this case, the expression equals 1 only if A=1 and B+CD=1 because

$A(B+CD) = 1 \cdot 1 = 1$

- Evaluating the expression (cont')

- Now, determine when B+CD term equals 1.

- The term B+CD=1 if either B=1 or CD=1 or if both

B and CD equal 1 because

B+CD = 1+0 = 1B+CD = 0+1 = 1

*B+CD* = 1+1 = 1

• The term *CD=1* only if *C=1* and *D=1* ENGINEERING COLLEGE

- Evaluating the expression (cont')

- Summary:

- A(B+CD)=1

- When A=1 and B=1 regardless of the values of C and D

- When A=1 and C=1 and D=1 regardless of the value of B

- The expression A(B+CD)=0 for all other value combinations of the variables.

Putting the results in truth table format

A(B+CD)=1

> When A=1 and B=1 regardless of the values of C and D When A=1 and C=1 and D=1 regardless of the value of B

|    |   | OUTPUT |   |   |          |

|----|---|--------|---|---|----------|

|    | A | В      | С | D | A (B+CD) |

| 1  | 0 | 0      | 0 | 0 | 0        |

| 5  | 0 | 0      | 0 | 1 | 0        |

| 7  | 0 | 0      | 1 | 0 | 0        |

|    | 0 | 0      | 1 | 1 | 0        |

|    | 0 | 1      | 0 | 0 | 0        |

|    | 0 | 1      | 0 | 1 | 0        |

| B  | 0 | 1      | 1 | 0 | 0        |

|    | 0 | 1      | 1 | 1 | 0        |

|    | 1 | 0      | 0 | 0 | 0        |

|    | 1 | 0      | 0 | 1 | 0        |

| X  | 1 | 0      | 1 | 0 | 0        |

|    | 1 | 0      | 1 | 1 | 1        |

| 1  | 1 | 1      | 0 | 0 | 1        |

| Υ. | 1 | 1      | 0 | 1 | 1        |

| 2  |   |        |   |   |          |

| S  | 1 | 1      | 1 | 1 | 1        |

- Karnaugh Maps

Boolean algebra helps us simplify expressions and circuits

- Karnaugh Map: A graphical technique for simplifying a Boolean expression into either form:

- minimal sum of products (MSP)

- minimal product of sums (MPS)

- Goal of the simplification.

- There are a minimal number of product/sum terms

- Each term has a minimal number of literals

- Circuit-wise, this leads to a minimal two-level implementation **ARED** ENGINEERING COLLEGE

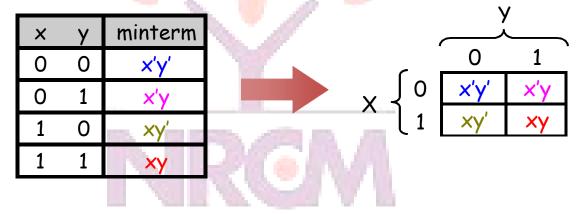

# Re-arranging the Truth Table

A two-variable function has four possible minterms. We can rearrange

these minterms into a Karnaugh map

- Now we can easily see which minterms contain common literals

- Minterms on the left and right sides contain y' and y respectively

- Minterms in the top and bottom rows contain x' and x respectively

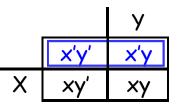

# Karnaugh Map Simplifications Imagine a two-variable sum of minterms:

Both of these minterms appear in the top row of a Karnaugh map, which

x'y' + x'y

means that they both contain the literal x'

x'y' + x'y = x'(y' + y) [Distributive] = x' • 1 [y + y' = 1] = x' [x • 1 = x]

What happens if you simplify this expression using Boolean algebra?

ENGINEERING COLLEGE

## More Two-Variable Examples

- Another example expression is x'y + xy

- Both minterms appear in the right side, where y is uncomplemented

x'y'

- Thus, we can reduce x'y + xy to just y

- How about x'y' + x'y + xy?

- We have x'y' + x'y in the top row, corresponding to x'

- There's also x'y + xy in the right side, corresponding to y

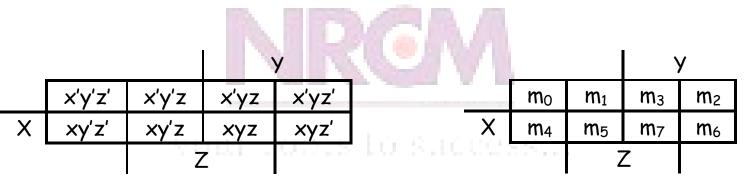

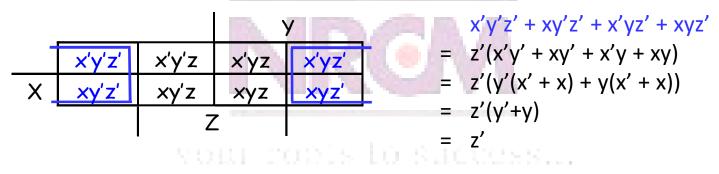

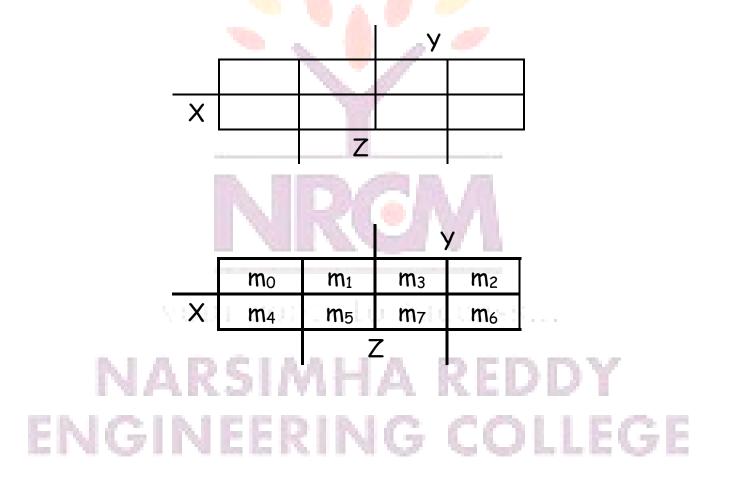

# A Three-Variable Karnaugh Map

For a three-variable expression with inputs x, y, z, the arrangement of

winterms is more tricky:

minterms is more tricky:

|     | ΥZ     |       |      |       | 0   |

|-----|--------|-------|------|-------|-----|

|     | 00     | 01    | 11   | 10    | X 1 |

| v 0 | x'y'z' | x'y'z | x'yz | x'yz' |     |

| ^ 1 | xy'z'  | xyʻz  | xyz  | xyz'  |     |

|   | 00             | 01    | 11             | 10             |  |

|---|----------------|-------|----------------|----------------|--|

| 0 | m <sub>0</sub> | $m_1$ | m <sub>3</sub> | m <sub>2</sub> |  |

| 1 | <b>m</b> 4     | $m_5$ | <b>m</b> 7     | <b>m</b> 6     |  |

Another way to label the K-map (use whichever you like):

# Why the funny ordering?

With this ordering, any group of 2, 4 or 8 adjacent squares on the map contains common literals that can be factored out

• "Adjacency" includes wrapping around the left and right sides:

We'll use this property of adjacent squares to do our simplifications.

ENGINEERING COLLEGE

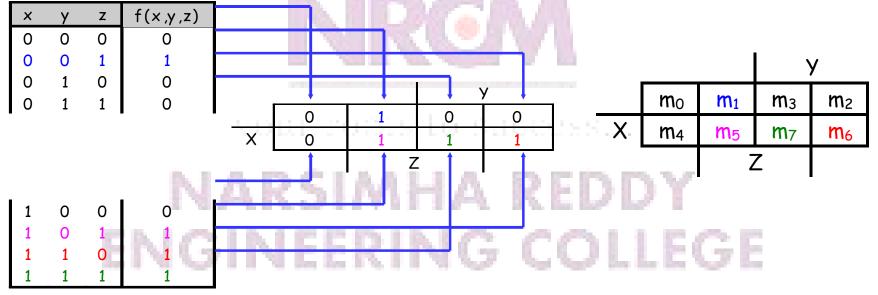

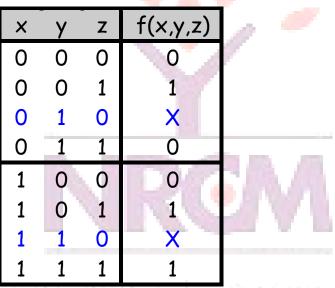

# K-maps From Truth Tables

- We can fill in the K-map directly from a truth table

- The output in row *i* of the table goes into square *m<sub>i</sub>* of the K-map

- Remember that the rightmost columns of the K-map are "switched"

# Reading the MSP from the K-map

- You can find the minimal SoP expression

- Each rectangle corresponds to one product term

- The product is determined by finding the common literals in that

# Grouping the Minterms Together

- The most difficult step is grouping together all the 1s in the K-map

- Make rectangles around groups of one, two, four or eight 1s

- All of the 1s in the map should be included in at least one rectangle

- Do not include any of the 0s

- Each group corresponds to one product term

# For the Simplest Result

- Make as few rectangles as possible, to minimize the number of products in the final expression.

- Make each rectangle as large as possible, to minimize the number of literals in each term.

- Rectangles can be overlapped, if that makes them larger.

your roots to success...

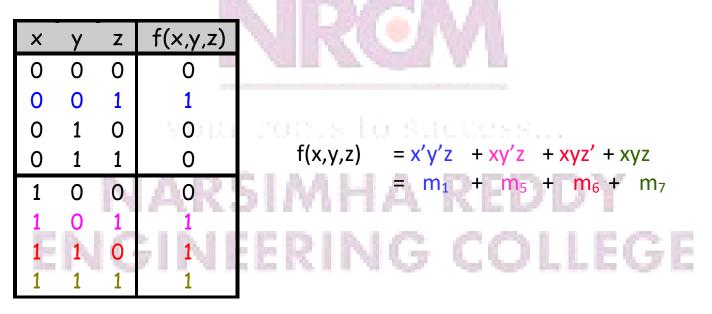

### K-map Simplification of SoP Expressions

- Let's consider simplifying f(x,y,z) = xy + y'z + xz

- You should convert the expression into a sum of minterms form,

- The easiest way to do this is to make a truth table for the function, and then read off the minterms

- You can either write out the literals or use the minterm shorthand

- Here is the truth table and sum of minterms for our example:

# Unsimplifying Expressions

- You can also convert the expression to a sum of minterms with Boolean algebra

- Apply the distributive law in reverse to add in missing variables.

- Very few people actually do this, but it's occasionally useful.

$$\begin{aligned} xy + y'z + xz &= (xy \bullet 1) + (y'z \bullet 1) + (xz \bullet 1) \\ &= (xy \bullet (z' + z)) + (y'z \bullet (x' + x)) + (xz \bullet (y' + y)) \\ &= (xyz' + xyz) + (x'y'z + xy'z) + (xy'z + xyz) \\ &= xyz' + xyz + x'y'z + xy'z \\ &= m_1 + m_5 + m_6 + m_7 \end{aligned}$$

- In both cases, we're actually "unsimplifying" our example expression

- The resulting expression is larger than the original one!

- But having all the individual minterms makes it easy to combine them together with the K-map

# Making the Example K-map

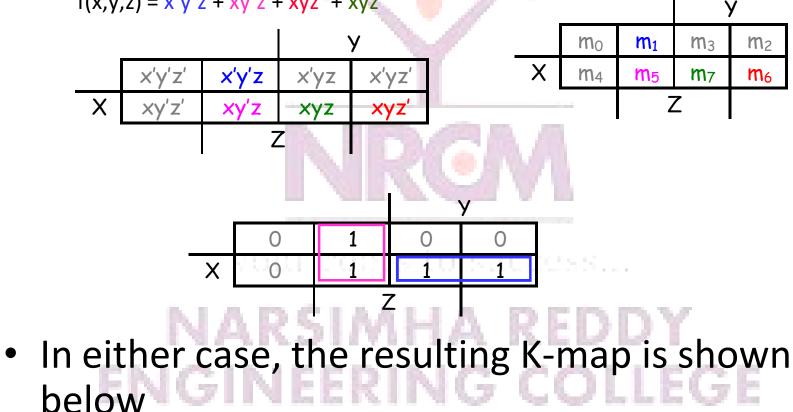

• In our example, we can write f(x,y,z) in two equivalent ways  $f(x,y,z) = m_1 + m_5 + m_6 + m_7$

f(x,y,z) = x'y'z + xy'z + xyz' + xyz

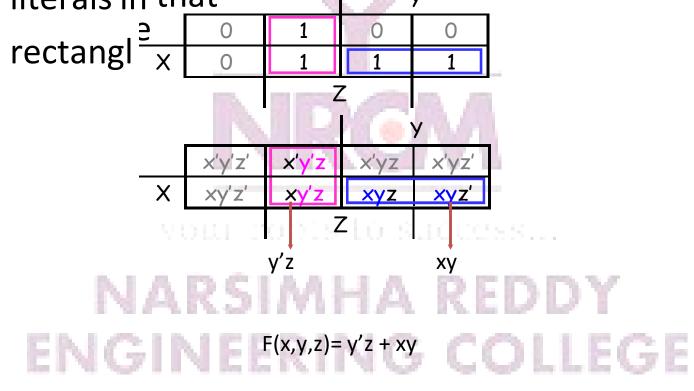

# Practice K-map 1

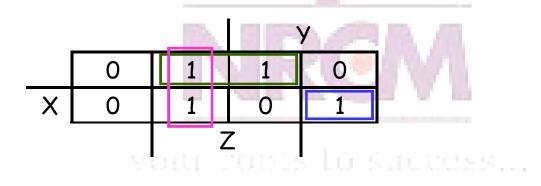

• Simplify the sum of minterms  $m_1 + m_3 + m_5 + m_6$

# Solutions for Practice K-map 1

- Here is the filled in K-map, with all groups shown

- The magenta and green groups overlap, which makes each of them as

- large as possible

- Minterm m<sub>6</sub> is in a group all by its lonesome

The final MSP here is x'z + y'z + xyz'

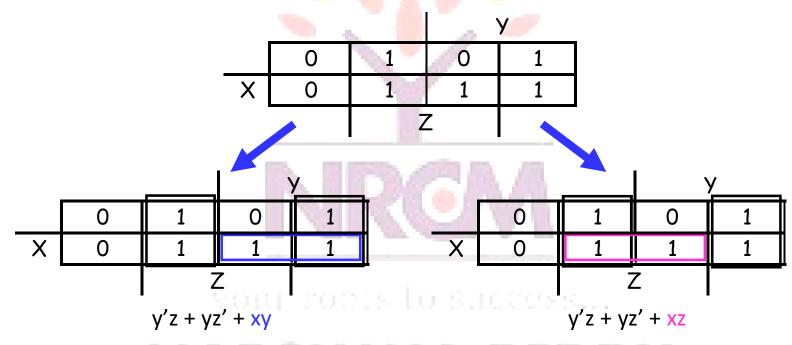

# • There may not necessarily be a *unique* MSP. The K-map below yields two

valid and equivalent MSPs, because there are two possible ways to include minterm m<sub>7</sub>

• Remember that overlapping groups is possible, as shown above

# ENGINEERING COLLEGE

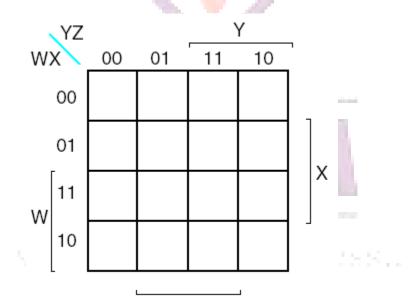

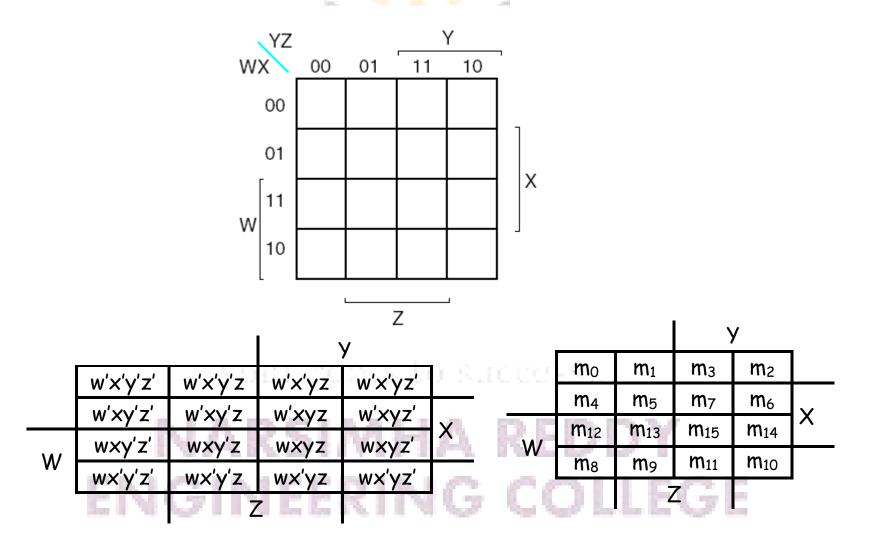

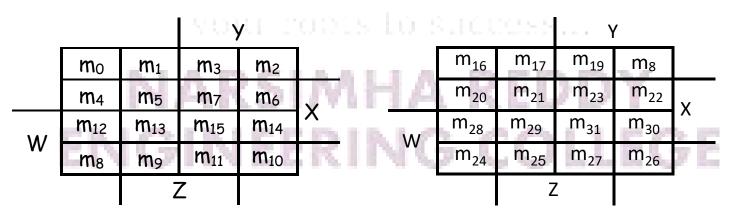

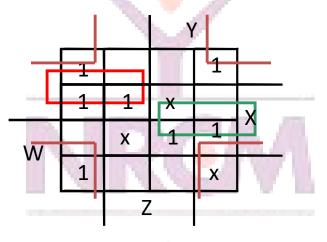

# Four-variable K-maps – f(W,X,Y,Z)

- We can do four-variable expressions too!

- The minterms in the third and fourth columns, and in the third and fourth rows, are switched around.

- Again, this ensures that adjacent squares have common literals

- Grouping minterms is similar to the three-variable case, but:

- You can have rectangular groups of 1, 2, 4, 8 or 16 minterms

- You can wrap around *all four* sides

# Four-variable K-maps

81

### Example: Simplify $m_0+m_2+m_5+m_8+m_{10}+m_{13}$

The expression is already a sum of minterms, so here's the Kmap:

We can make the following groups, resulting in the MSP x'z' + xy'z

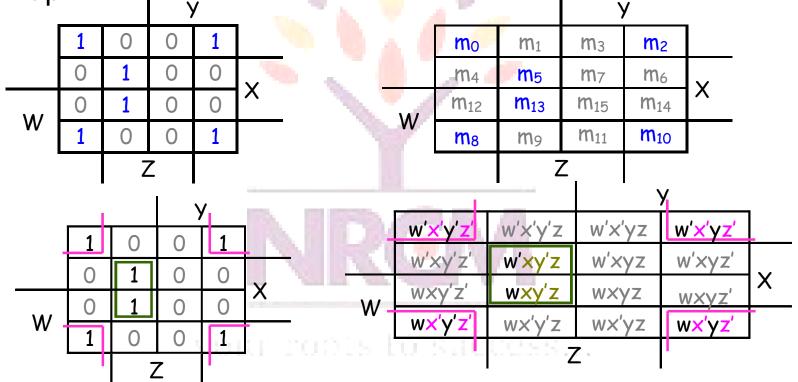

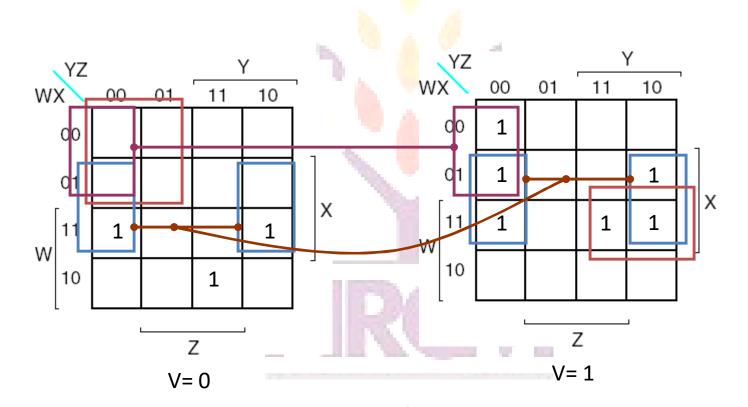

# Five-variable K-maps – f(V,W,X,Y,Z)

### Simplify f(V,W,X,Y,Z)=Σm(0,1,4,5,6,11,12,14,16,20,22,28,30,31)

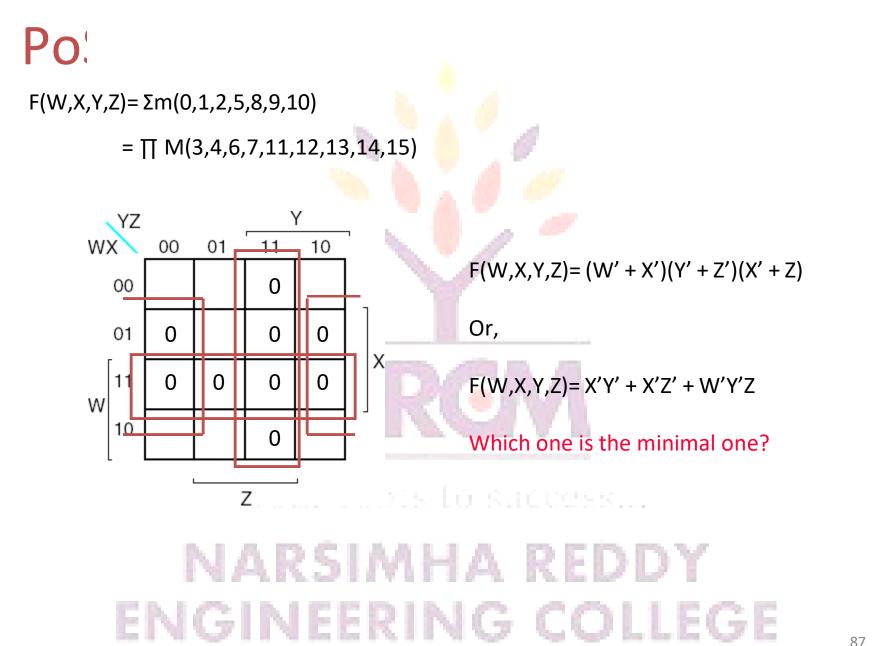

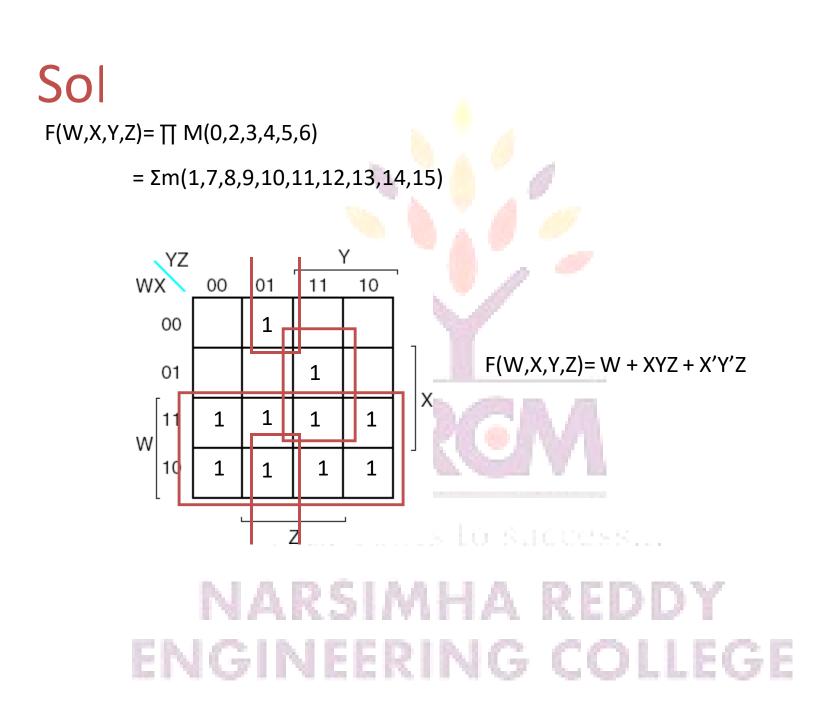

# Po

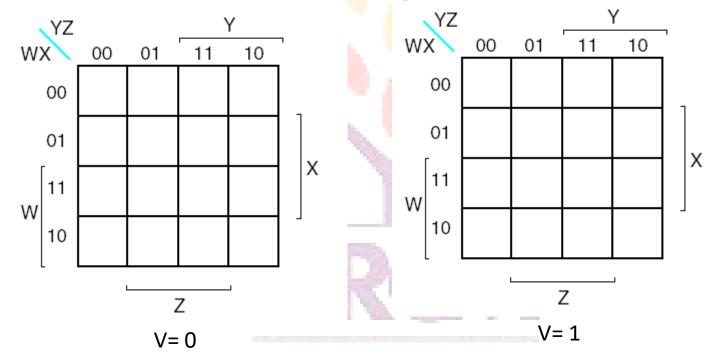

Maxterms are grouped to find minimal PoS expression 00

Maxterms are grouped to find minimal PoS

| х | 0 | x +y+z  | x+y+z'  | x+y'+z'  | x+y'+z  |

|---|---|---------|---------|----------|---------|

|   | 1 | x' +y+z | x'+y+z' | x'+y'+z' | x'+y'+z |

your roots to success...

#### Po • $F(W,X,Y,Z) = \prod M(0,1,2,4,5)$ у<u>г</u> 11 01 10 00 x+y'+z' x+y+z x+y'+z 0 +V+ZХ x'+y'+z' x'+y'+z x'+y+z' +y+z 1

F(W,X,Y,Z) = Y . (X + Z)У<u>7</u> 11 10 00 01 0 0 1 0 0 Х 0 0 1 1 1

# ld

- You don't always need all 2<sup>n</sup> input combinations in an n-variable function

- If you can guarantee that certain input combinations never occur

- If some outputs aren't used in the rest of the circuit

- We mark don't-care outputs in truth tables and K-maps with Xs.

• Within a K-map, each X can be considered as either 0 or 1. You should pick the interpretation that allows for the most simplification.

# ENGINEERING COLLEGE

### Pra

Find a MSP for

$f(w,x,y,z) = \sum m(0,2,4,5,8,14,15), d(w,x,y,z) = \sum m(7,10,13)$

This notation means that input combinations wxyz = 0111, 101 Pand 1101 × (corresponding to minterms m<sub>7</sub>, m<sub>10</sub> and m<sub>13</sub>) are unused.

# Solutions for Practice K-map

• Find a MSP for:  $f(w,x,y,z) = \sum m(0,2,4,5,8,14,15), d(w,x,y,z) = \sum m(7,10,13)$

f(w,x,y,z) = x'z' + w'xy' + wxy

# K-map Summary

- K-maps are an alternative to algebra for simplifying expressions

- The result is a MSP/MPS, which leads to a minimal two-level circuit

- It's easy to handle don't-care conditions

- K-maps are really only good for manual simplification of small expressions...

- Things to keep in mind:

- Remember the correct order of minterms/maxterms on the K-map

- When grouping, you can wrap around all sides of the K-map, and your groups can overlap

- Make as few rectangles as possible, but make each of them as large as possible. This leads to fewer, but simpler, product terms

- There may be more than one valid solution

# ENGINEERING COLLEGE

### Tabulation Method – **STEP 1**

- 1. Partition Prime Implicants (or minterms) According to Number of 1's

- 2. Check Adjacent Classes for Cube Merging Building a New List

- 3. If Entry in New List Covers Entry in Current List Disregard Current List Entry

- 4. If Current List = New List HALT Else Current List ← New List New List ← NULL Go To Step 1 ENGINEERING COLLEGE

$f^{on} = \{m_0, m_1, m_2, m_3, m_5, m_8, m_{10}, m_{11}, m_{13}, m_{15}\} = \sum (0, 1, 2, 3, 5, 8, 10, 11, 13, 15)$

| Minterm |   | Cu | ıbe |   |

|---------|---|----|-----|---|

| 0       | 0 | 0  | 0   | 0 |

| 1       | 0 | 0  | 0   | 1 |

| 2       | 0 | 0  | 1   | 0 |

| 8       | 1 | 0  | 0   | 0 |

| 3       | 0 | 0  | 1   | 1 |

| 5       | 0 | 1  | 0   | 1 |

| 10      | 1 | 0  | 1   | 0 |

| 11      | 1 | 0  | 1   | 1 |

| 13      | 1 | 1  | 0   | 1 |

| 15      | 1 | 1  | 1   | 1 |

### your roots to success...

$f^{on} = \{m_0, m_1, m_2, m_3, m_5, m_8, m_{10}, m_{11}, m_{13}, m_{15}\} = \sum (0, 1, 2, 3, 5, 8, 10, 11, 13, 15)$

L 7 A 7 J

|         |   |    |    |   | _            |         |     |    |     | - 10 | 1   |

|---------|---|----|----|---|--------------|---------|-----|----|-----|------|-----|

| Minterm |   | Cu | be |   |              | Minterm |     | Cu | ıbe | 199  |     |

| 0       | 0 | 0  | 0  | 0 | $\checkmark$ | 0,1     | 0   | 0  | 0   | -    |     |

| 1       | 0 | 0  | 0  | 1 | $\checkmark$ | 0,2     | 0   | 0  | -   | 0    |     |

| 2       | 0 | 0  | 1  | 0 | $\checkmark$ | 0,8     |     | 0  | 0   | 0    |     |

| 8       | 1 | 0  | 0  | 0 | $\checkmark$ | 1,3     | 0   | 0  | H   | 1    |     |

| 3       | 0 | 0  | 1  | 1 | $\checkmark$ | 1,5     | 0   |    | 0   | 1    |     |

| 5       | 0 | 1  | 0  | 1 | $\checkmark$ | 2,3     | 0   | 0  | 1   | -    |     |

| 10      | 1 | 0  | 1  | 0 | $\checkmark$ | 2,10    | -   | 0  | 1   | 0    |     |

| 11      | 1 | 0  | 1  | 1 | $\checkmark$ | 8,10    | 1   | 0  | -   | 0    |     |

| 13      | 1 | 1  | 0  | 1 | $\checkmark$ | 3,11    | - 1 | 0  | 1   | 1    |     |

| 15      | 1 | 1  | 1  | 1 | $\checkmark$ | 5,13    | - 1 | 1  | 0   | 1    |     |

|         |   |    |    |   |              | 10,11   | 1   | 0  | 1   |      | V B |

|         |   |    |    |   |              | 11,15   | 1   | -  | 1   | 1    |     |

|         |   |    |    |   |              | 13,15   | 1   | 1  | ÷   | 1    |     |

$f^{on} = \{m_0, m_1, m_2, m_3, m_5, m_8, m_{10}, m_{11}, m_{13}, m_{15}\} = \sum (0, 1, 2, 3, 5, 8, 10, 11, 13, 15)$

N 7 🔺 🧉 🍃

|         | 1 | ~  | -   |   | 1            | 2.61    | 1   | ~   |       |   |              |           | 1 |    |     |   |

|---------|---|----|-----|---|--------------|---------|-----|-----|-------|---|--------------|-----------|---|----|-----|---|

| Minterm |   | Cu | ıbe |   |              | Minterm |     | Cu  | ıbe   | 1 |              | Minterm   |   | Cu | ıbe |   |

| 0       | 0 | 0  | 0   | 0 | $\checkmark$ | 0,1     | 0   | 0   | 0     | - | ~            | 0,1,2,3   | 0 | 0  | -   | - |

| 1       | 0 | 0  | 0   | 1 | $\checkmark$ | 0,2     | 0   | 0   | -     | 0 | $\checkmark$ | 0,8,2,10  | - | 0  | -   | 0 |

| 2       | 0 | 0  | 1   | 0 | $\checkmark$ | 0,8     | -   | 0   | 0     | 0 | ~            | 2,3,10,11 | - | 0  | 1   | - |

| 8       | 1 | 0  | 0   | 0 | $\checkmark$ | 1,3     | 0   | 0   | đ     | 1 | $\checkmark$ |           |   |    |     |   |

| 3       | 0 | 0  | 1   | 1 | $\checkmark$ | 1,5     | 0   | -   | 0     | 1 |              |           |   |    |     |   |

| 5       | 0 | 1  | 0   | 1 | $\checkmark$ | 2,3     | 0   | 0   | 1     | - | $\checkmark$ |           |   |    |     |   |

| 10      | 1 | 0  | 1   | 0 | $\checkmark$ | 2,10    | -   | 0   | 1     | 0 | $\checkmark$ |           |   |    |     |   |

| 11      | 1 | 0  | 1   | 1 | $\checkmark$ | 8,10    | 1   | 0   | -     | 0 | $\checkmark$ |           |   |    |     |   |

| 13      | 1 | 1  | 0   | 1 | $\checkmark$ | 3,11    | - 1 | 0   | 1     | 1 | ~            |           |   |    |     |   |

| 15      | 1 | 1  | 1   | 1 | $\checkmark$ | 5,13    | 1.5 | 1   | 0     | 1 | 67 B.        |           |   |    |     |   |

|         |   |    |     |   |              | 10,11   | 1   | 0   | 1     |   | $\checkmark$ |           |   |    |     |   |

|         |   |    |     |   |              | 11,15   | 1   | -   | 1     | 1 |              |           |   |    |     |   |

|         |   |    |     |   |              | 13,15   | 1   | 1   |       | 1 |              |           |   |    |     |   |

|         |   |    |     |   |              |         |     | 1.1 | 1.1.1 |   |              |           |   |    |     |   |

$f^{on} = \{m_0, m_1, m_2, m_3, m_5, m_8, m_{10}, m_{11}, m_{13}, m_{15}\} = \sum (0, 1, 2, 3, 5, 8, 10, 11, 13, 15)$

N 7 🔺 7 🖬

| Minterm |   | Cu | be |   |              | Minterm |   | Cu | ıbe | P |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Minterm   |   | Cu | be |   |      |

|---------|---|----|----|---|--------------|---------|---|----|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|----|----|---|------|

| 0       | 0 | 0  | 0  | 0 | $\checkmark$ | 0,1     | 0 | 0  | 0   | - | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0,1,2,3   | 0 | 0  | _  | _ | PI=A |

| 1       | 0 | 0  | 0  | 1 | $\checkmark$ | 0,2     | 0 | 0  |     | 0 | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0,8,2,10  | - | 0  | -  | 0 | PI=C |

| 2       | 0 | 0  | 1  | 0 | $\checkmark$ | 0,8     | - | 0  | 0   | 0 | <ul> <li>Image: A start of the start of</li></ul> | 2,3,10,11 | - | 0  | 1  | - | PI=B |

| 8       | 1 | 0  | 0  | 0 | $\checkmark$ | 1,3     | 0 | 0  | đ   | 1 | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |   |    |    |   |      |

| 3       | 0 | 0  | 1  | 1 | ✓            | 1,5     | 0 | 2  | 0   | 1 | PI=D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |   |    |    |   |      |

| 5       | 0 | 1  | 0  | 1 | $\checkmark$ | 2,3     | 0 | 0  | 1   | - | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |   |    |    |   |      |

| 10      | 1 | 0  | 1  | 0 | <b>√</b>     | 2,10    | _ | 0  | 1   | 0 | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |   |    |    |   |      |

| 11      | 1 | 0  | 1  | 1 | V            | 8,10    | 1 | 0  | -   | 0 | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |   |    |    |   |      |

| 13      | 1 | 1  | 0  | 1 | <b>√</b>     | 3,11    |   | 0  | 1   | 1 | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |   |    |    |   |      |

| 15      | 1 | 1  | 1  | 1 | $\checkmark$ | 5,13    | 1 | 1  | 0   | 1 | PI=E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |   |    |    |   |      |

|         |   |    |    |   |              | 10,11   | 1 | 0  | 1   | - | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |   |    |    |   |      |

|         |   |    |    |   |              | 11,15   | 1 | -  | 1   | 1 | PI=F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |   |    |    |   |      |

|         |   |    |    |   |              | 13,15   | 1 | 1  | γ÷. | 1 | PI=G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s         |   |    |    |   |      |

f<sup>on</sup> = {A,B,C,D,E,F,G} = {00--, -01-, -0-0, 0-01, -101, 1-11, 11-1} ENGINEERING COLLEGE

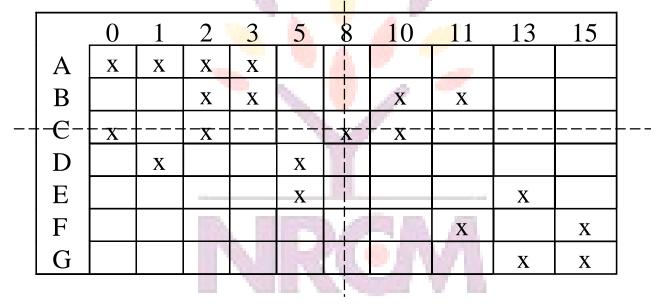

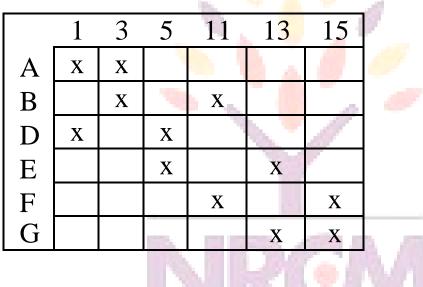

### OTED O Construct Cover Table

- Pls Along Vertical Axis (in order of # of literals)

- Minterms Along Horizontal Axis

|   | 0 | 1 | 2 | 3 | 5 | 8 | 10 | 11 | 13 | 15 |

|---|---|---|---|---|---|---|----|----|----|----|

| А | X | X | X | X | 1 |   | 1  | 6  |    |    |

| В |   |   | X | X |   | P | X  | X  |    |    |

| С | X |   | X |   |   | X | X  |    |    |    |

| D |   | X |   |   | X |   | -  |    |    |    |

| E |   |   |   | A | X |   | 2  | ЪЛ | X  |    |

| F |   |   |   |   |   | 1 | S  | X  |    | X  |

| G |   |   |   |   |   |   |    |    | X  | X  |

vour roots lo successi...

# NOTE: Table 4.2 in book is incomplete

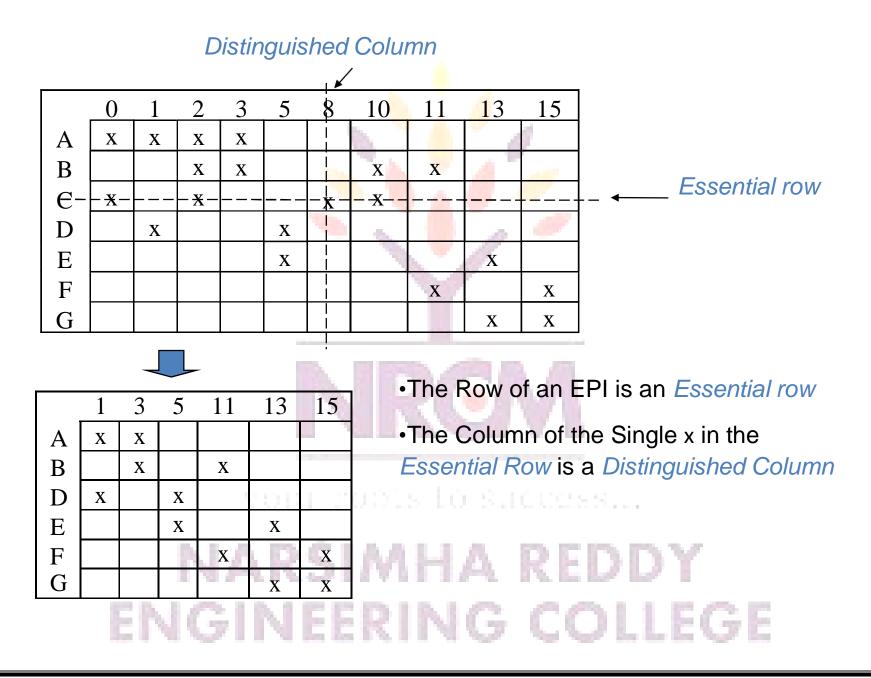

### CTCDO Cinding the Minimum Cover

- Extract All Essential Prime Implicants, EPI

- EPIs are the PI for which a Single x Appears in a Column

- *C* is an EPI so: *f* <sup>on</sup>={*C*, ...}

- Row C and Columns 0, 2, 8, and 10 can be Eliminated Giving Reduced Cover Table

- Examine Reduced Table for New EPIs

# ENGINEERING COLLEGE

#### OTED O Deduced Teble

## **Row and Column Dominance**

- If Row P has x's Everywhere Row Q Does Then Q Dominates P if P has fewer x's

- If Column *i* has x's Everywhere *j* Does Then *j* Dominates *i* if *i* has fewer x's

- If Row P is equal to Row Q and Row Q does not cost more than Row P, eliminate Row P, or if Row P is dominated by Row Q and Row Q Does not cost more than Row P, eliminate Row P

- If Column *i* is equal to Column *j*, eliminate Column *i* or if Column *i* dominates Column *j*, eliminate Column *i* REDDY

ENGINEERING COLLEGE

### STEP 3 – The Reduced Cover Table

Initially, Columns 0, 2, 8 and 10 Removed

- No EPIs are Present

- No Row Dominance Exists

- No Column Dominance Exists

- This is *Cyclic Cover* Table

- Must Solve Exactly OR Use a Heuristic

ENGINEERING COLLEGE

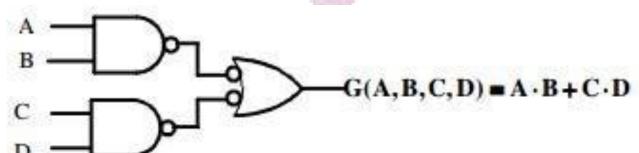

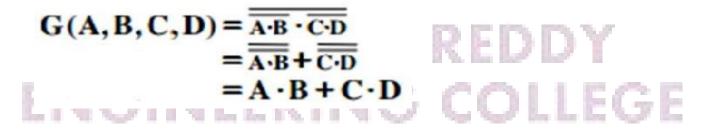

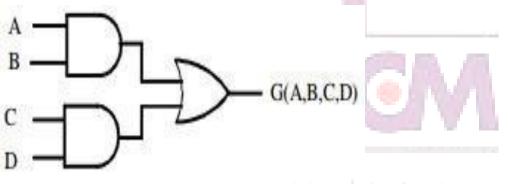

# NAND Function Implementation

NAND gates can implement a simplified SumofProducts form. Constructing two level NAND-NAND gate circuits

The first level is two 2-input NAND gates using ANDInvert. The second level is one 2-input NAND gate using Invert-OR. Using the NAND relationship, we

# Logic Family Characteristics

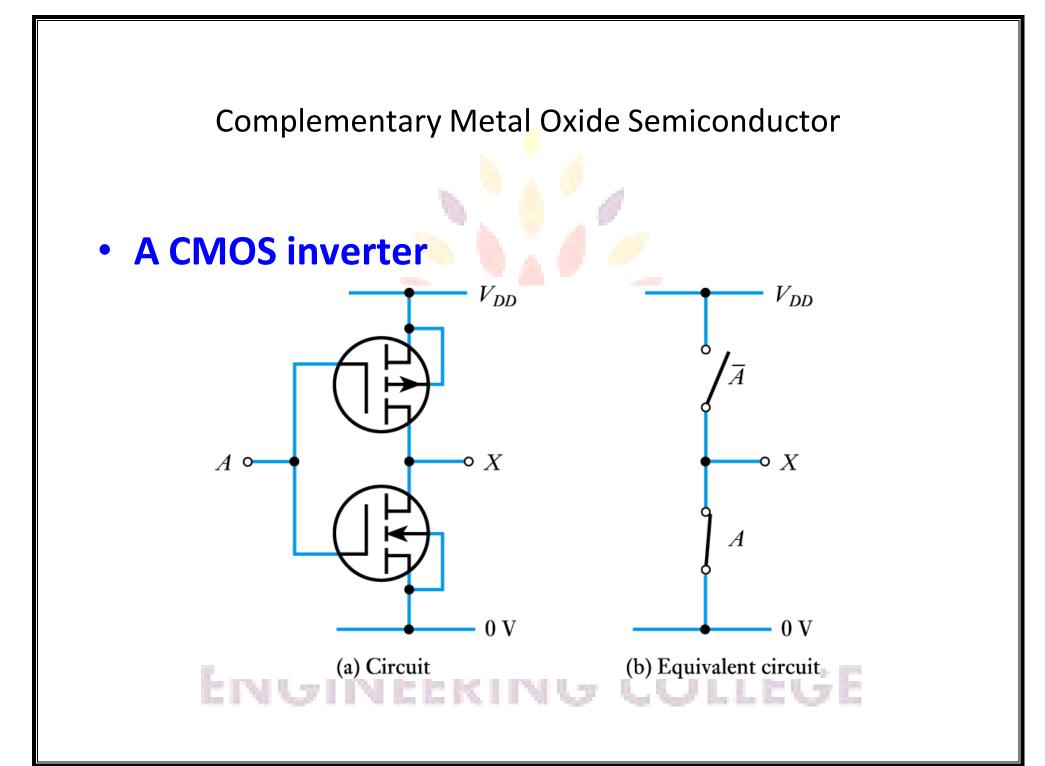

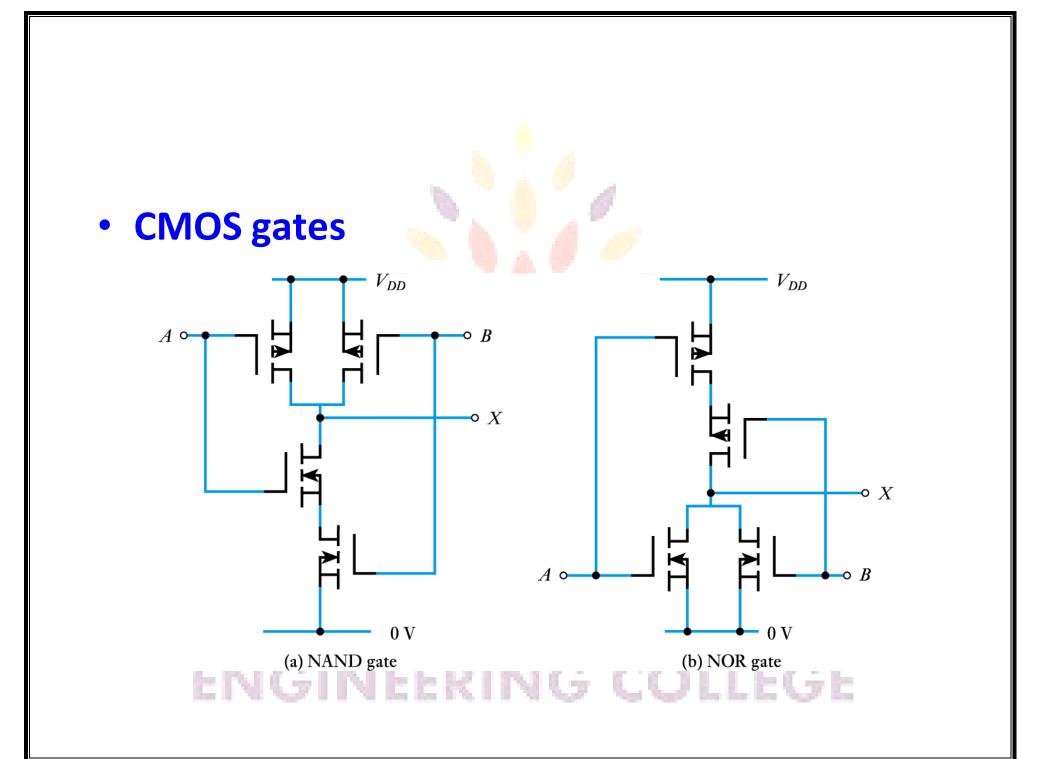

- Complementary metal oxide semiconductor (CMOS)

- most widely used family for large-scale devices

- combines high speed with low power consumption

- usually operates from a single supply of 5 15 V

- excellent noise immunity of about 30% of supply voltage

- can be connected to a large number of gates (about 50)

- many forms some with  $t_{PD}$  down to 1 ns

- power consumption depends on speed (perhaps 1 mW) ENGINEERING COLLEGE

# NAND Implementation (Cont.)

In the implementation, note that the bubbles are on opposite ends of the same line. Thus, they can be combined and deleted:

nour robis lo successi...

This form of the implementation is the Sum-of-Products form.

# NOR Gates

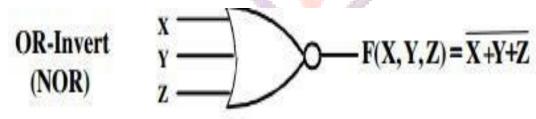

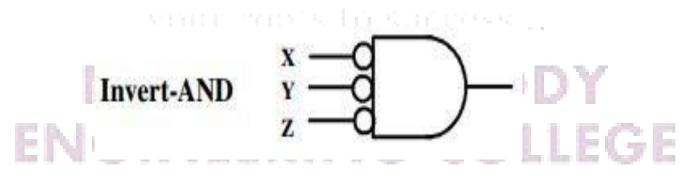

The basic positive logic NOR gate (Not-OR) is denoted by the following symbol:

This is called the OR-Invert, since it is logically an OR function followed by an invert. By DeMorgan's Law we have the following Invert-AND symbol for a NOR gate:

# General Implementations (Cont.)

Given a two level implementation desired, use the previous transfromations to get it into one of the below forms. Then follow the steps to transform the function to the desired form:

| For Type:                     | Use:                                                                                                       |

|-------------------------------|------------------------------------------------------------------------------------------------------------|

| AND-OR<br>(SOP Form)          | Circle 1's in the K-Map and minimize<br>(Also use for NAND-NAND)                                           |

| AND-NOR<br>(SOP complemented) | Circle 0's in the K-Map and minimize                                                                       |

| OR-AND<br>(POS Form)          | Circle 0's in the K-Map and minimize<br>SOP. Use DeMorgan's to transform to<br>POS. (Also use for NOR-NOR) |

| OR-NAND<br>(POS complemented) | Circle 1's in the K-Map and minimize<br>SOP. Use DeMorgan's to transform to<br>POS.                        |

the R. W. Noff, R. R. W. Der, Rev. R. W. H. W. Noff, "Not New York for the Noff In-

# Multi-level NAND Implementations

- Add inverters in two-level implementation into the cost picture

- Attempt to "combine" inverters to reduce the term count

- Attempt to reduce literal + tem count by factoring expression into POSOP or SOPOS

vour robis lo success...

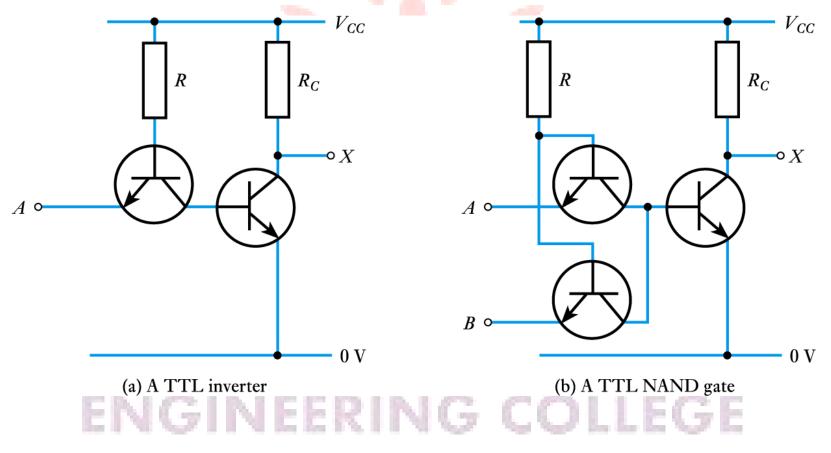

### Transistor-transistor logic (TTL)

- based on bipolar transistors

- one of the most widely used families for small- and medium-scale devices – rarely used for VLSI

- typically operated from 5V supply

- typical noise immunity about 1 1.6 V

- many forms, some optimised for speed, power, etc.

- high speed versions comparable to CMOS (~ 1.5 ns)

- low-power versions down to about 1 mW/gate ENGINEERING COLLEGE

### Emitter-coupled logic (ECL)

- based on bipolar transistors, but removes problems of storage time by preventing the transistors from saturating

- very fast operation propagation delays of 1ns or less

- high power consumption, perhaps 60 mW/gate

- low noise immunity of about 0.2-0.25 V

- used in some high speed specialist applications, but now largely replaced by high speed CMOS

ENGINEERING COLLEGE

# A Comparison of Logic Families

|                      | - Y., D I |           |        |

|----------------------|-----------|-----------|--------|

| Parameter            | CMOS      | TTL       | ECL    |

| Basic gate           | NAND/NOR  | NAND      | OR/NOR |

| Fan-out              | >50       | 10        | 25     |

| Power per gate (mW)  | 1 @ 1 MHz | 1 - 22    | 4 - 55 |

| Noise immunity       | Excellent | Very good | Good   |

| t <sub>PD</sub> (ns) | 1 - 200   | 1.5 – 33  | 1 - 4  |

| ENGINE               | ERING     | COLLEG    | GE     |

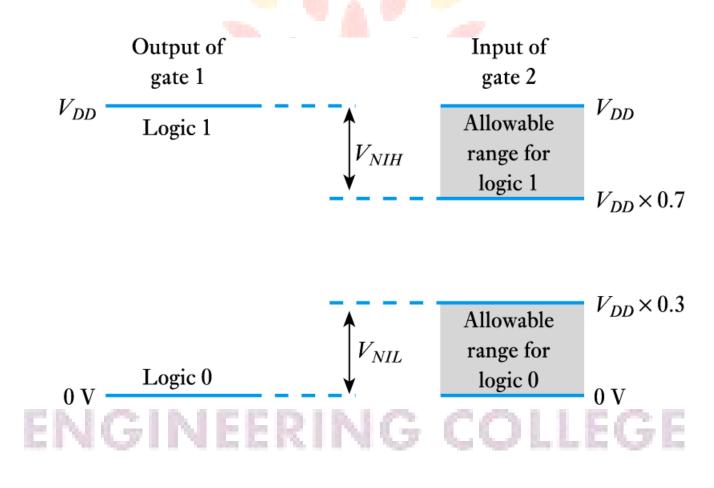

### CMOS logic levels and noise immunity

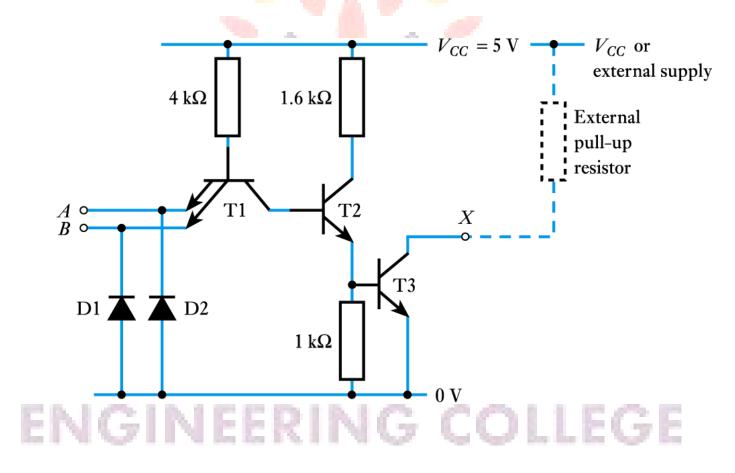

### Transistor-Transistor Logic

Discrete TTL inverter and NAND gate circuits

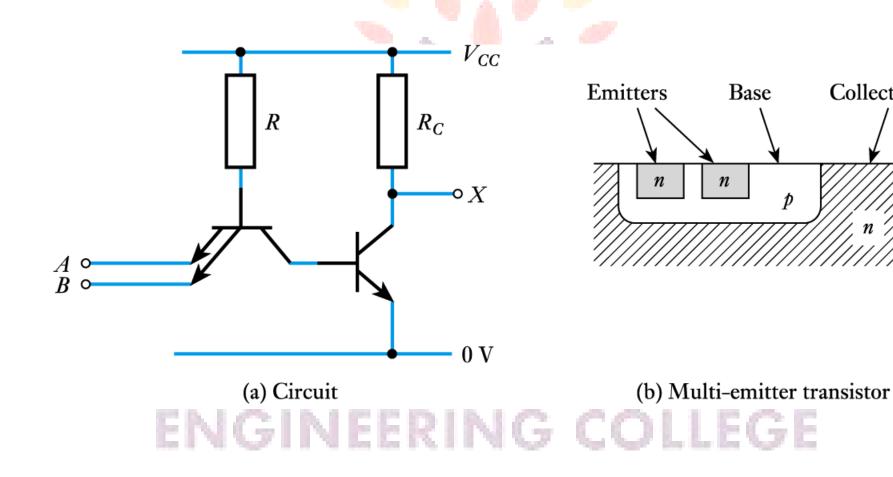

### A basic integrated circuit TTL NAND gate

Collector

Base

n

n

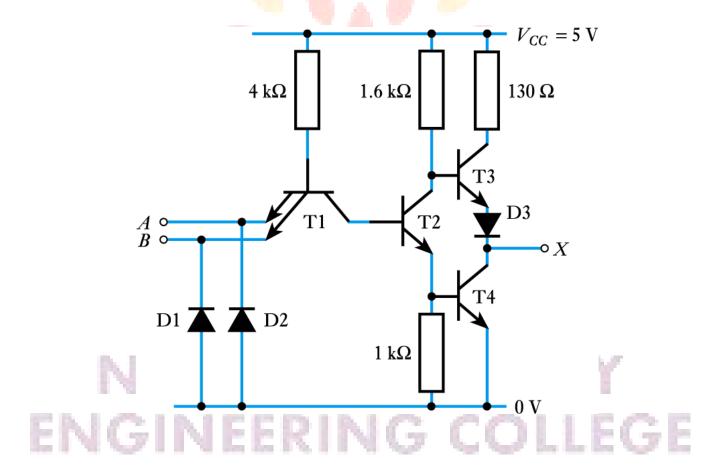

### • A standard TTL NAND gate

### A TTL NAND gate with open collector output

### **Combinational Logic**

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

Fig. 4-1 Block Diagram of Combinational Circuit

# Analysis procedure

To obtain the output Boolean functions from a logic diagram, proceed as follows:

- 1. Label all gate outputs that are a function of input variables with arbitrary symbols. Determine the Boolean functions for each gate output.

- 2. Label the gates that are a function of input variables and previously labeled gates with other arbitrary symbols. Find the Boolean functions for these gates.

- 3. Repeat the process outlined in step 2 until the outputs of the circuit are obtained.

- 4. By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables.

# NARSIMHA REDDY ENGINEERING COLLEGE

### Example

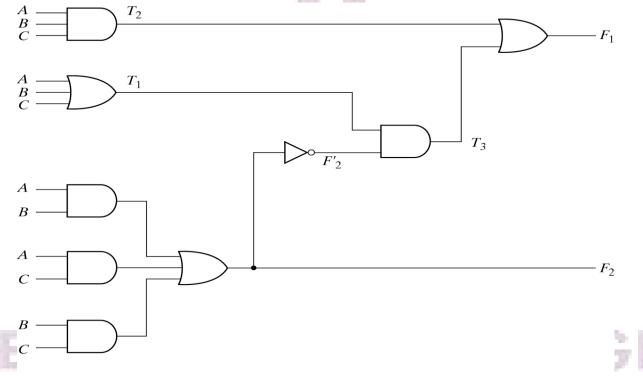

$F_2 = AB + AC + BC; T_1 = A + B + C; T_2 = ABC; T_3 = F_2'T_1;$  $F_1 = T_3 + T_2$

$F_1 = T_3 + T_2 = F_2'T_1 + ABC = A'BC' + A'B'C + AB'C' + ABC$

Fig. 4-2 Logic Diagram for Analysis Example

### Derive truth table from logic diagram

• We can derive the truth table in Table 4-1 by using the circuit of Fig.4-2.

Table 4-1

Truth Table for the Logic Diagram of Fig. 4-2

| A | В | С | F <sub>2</sub> | <b>F</b> '2 | <i>T</i> 1 | T <sub>2</sub> | T <sub>3</sub> | F1 |

|---|---|---|----------------|-------------|------------|----------------|----------------|----|

| 0 | 0 | 0 | 0              | 1           | 0          | 0              | 0              | 0  |

| 0 | 0 | 1 | 0              | 1           | 1          | 0              | 1              | 1  |

| 0 | 1 | 0 | 0              | 1           | 1          | 0              | 1              | 1  |

| 0 | 1 | 1 | 1              | 0           | 1          | 0              | 0              | 0  |

| 1 | 0 | 0 | 0              | 1           | 1          | 0              | 1              | 1  |

| 1 | 0 | 1 | 1              | 0           | 1          | 0              | 0              | 0  |

| 1 | 1 | 0 | 1              | 0           | 1          | 0              | 0              | 0  |

| 1 | 1 | 1 | 1              | 0           | 1          | 1              | 0              | 1  |

## Design procedure

1. Table4-2 is a Code-Conversion example, first, we can list the relation of the BCD and Excess-3 codes in the truth table.

Table 4.7

|   | Input | BCD |   | <b>Output Excess-3 Code</b> |   |   |   |  |

|---|-------|-----|---|-----------------------------|---|---|---|--|

| A | B     | с   | D | w                           | x | y | z |  |

| 0 | 0     | 0   | 0 | 0                           | 0 | 1 | 1 |  |

| 0 | 0     | 0   | 1 | 0                           | 1 | 0 | 0 |  |

| 0 | 0     | 1   | 0 | 0                           |   | 0 | 1 |  |

| 0 | 0     | 1   | 1 | 0                           | 1 | 1 | 0 |  |

| 0 | 1     | 0   | 0 | 0                           | 1 | 1 | 1 |  |

| 0 | 1     | 0   | 1 | 1                           | 0 | 0 | 0 |  |

| 0 | 1     | 1   | 0 | 1                           | 0 | 0 | 1 |  |

| 0 | 1     | 1   | 1 | 1                           | 0 | 1 | 0 |  |

| 1 | 0     | 0   | 0 | 1                           | 0 | 1 | 1 |  |

| 1 | 0     | 0   | 1 | 1                           | 1 | 0 | 0 |  |

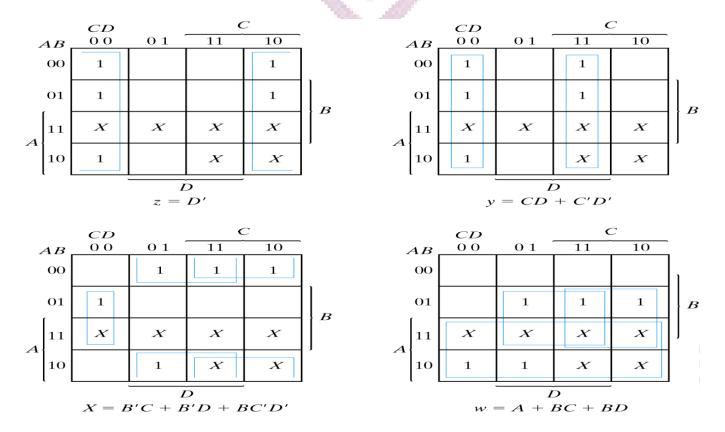

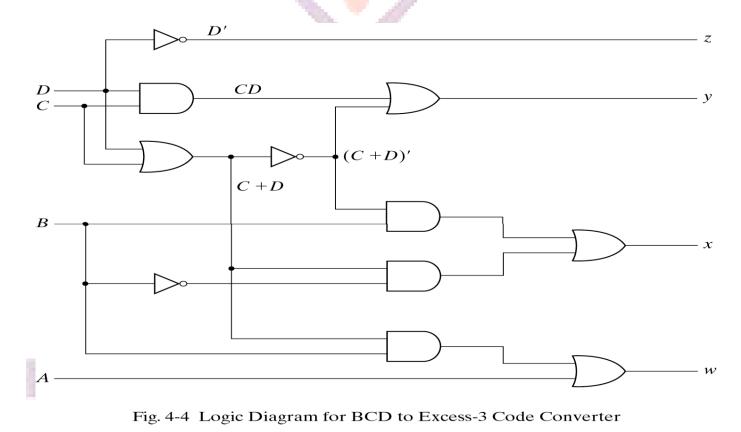

### Karnaugh map

2. For each symbol of the Excess-3 code, we use 1's to draw the map for simplifying Boolean function.

Fig. 4-3 Maps for BCD to Excess-3 Code Converter

124

$$z = D'; y = CD + C'D' = CD + (C + D)'$$

$x = B'C + B'D + BC'D' = B'(C + D) + B(C + D)'$

$w = A + BC + BD = A + B(C + D)$

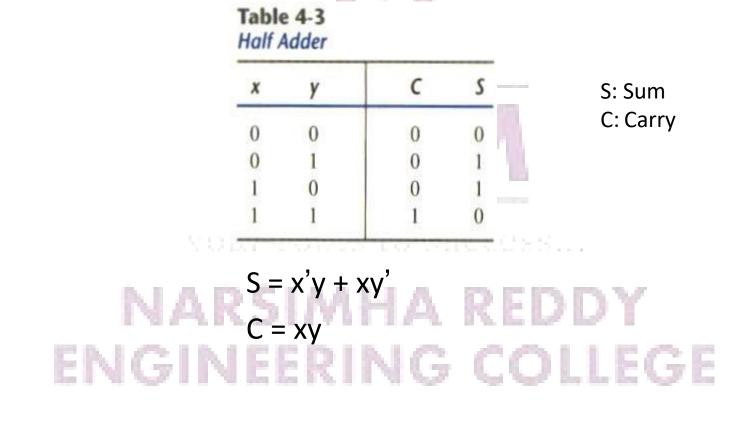

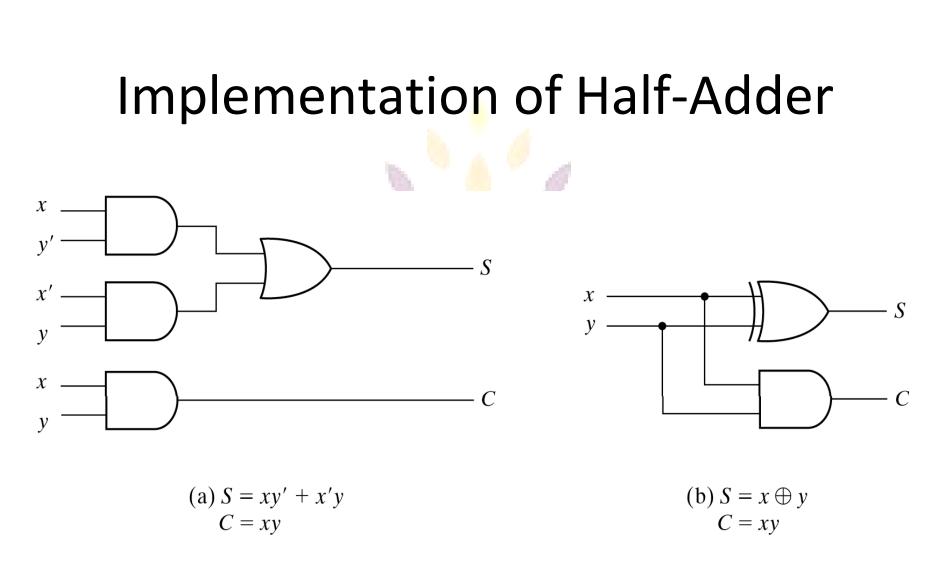

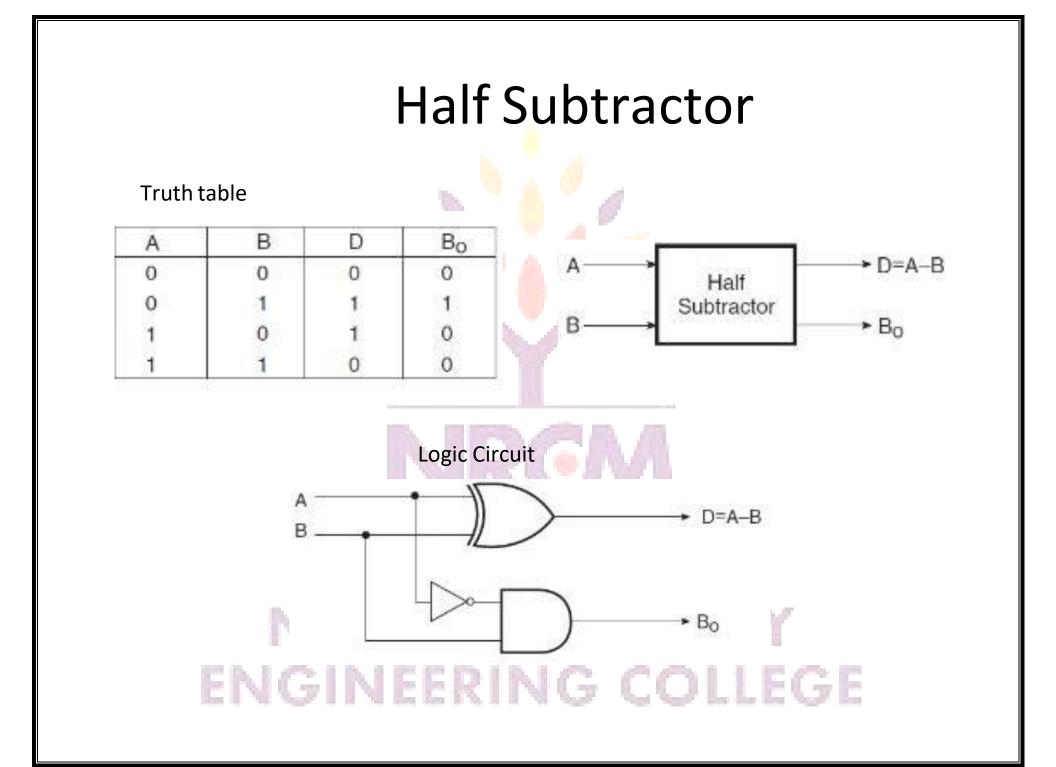

- A combinational circuit that performs the addition of two bits is called a half adder.

- The truth table for the half adder is listed below:

Fig. 4-5 Implementation of Half-Adder

# Full-Adder

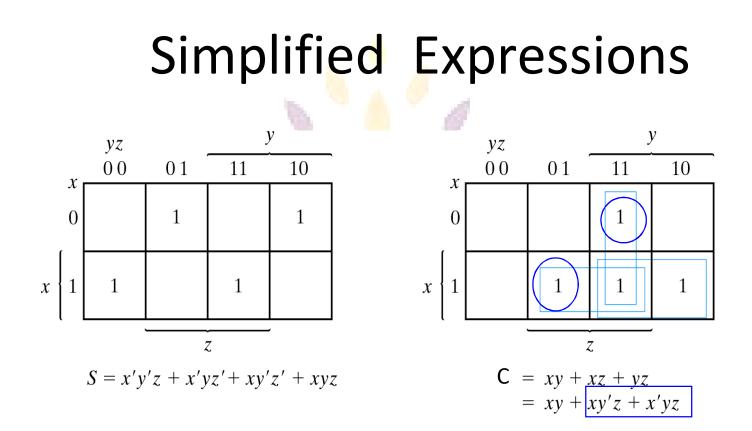

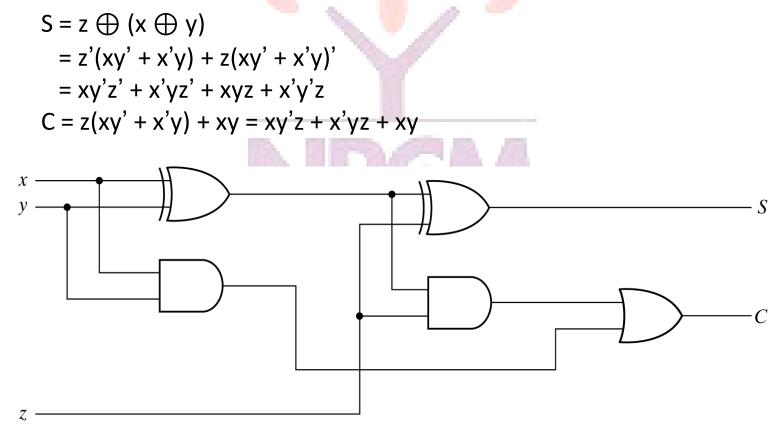

One that performs the addition of three bits(two significant bits and a previous carry) is a full adder.

#### Table 4-4 Full Adder

| x | Y | z | С | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Fig. 4-6 Maps for Full Adder

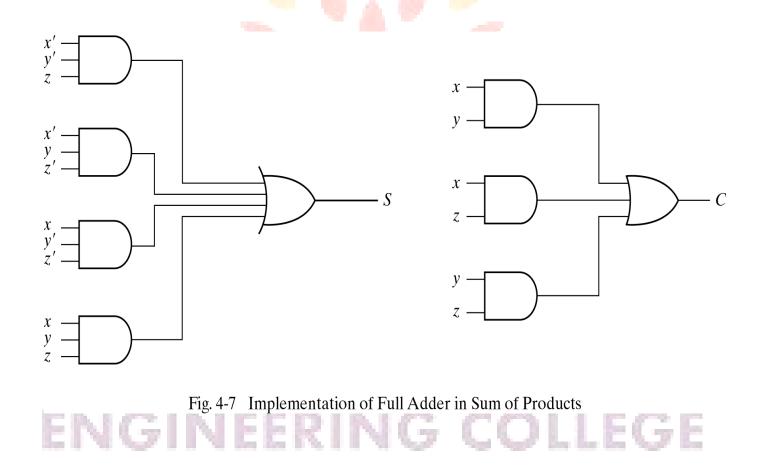

### S = x'y'z + x'yz' + xy'z' + xyzC = xy + xz + yz COLLEGE

# Full adder implemented in SOP

## Another implementation

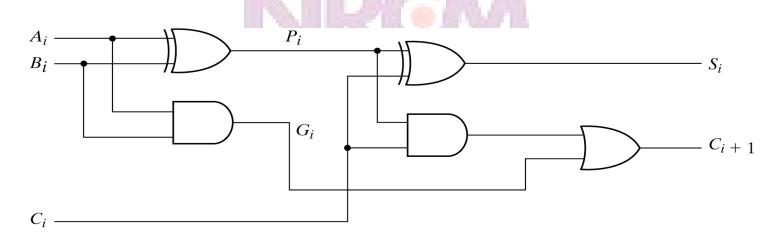

• Full-adder can also implemented with two half adders and one OR gate (Carry Look-Ahead adder).

Fig. 4-8 Implementation of Full Adder with Two Half Adders and an OR Gate

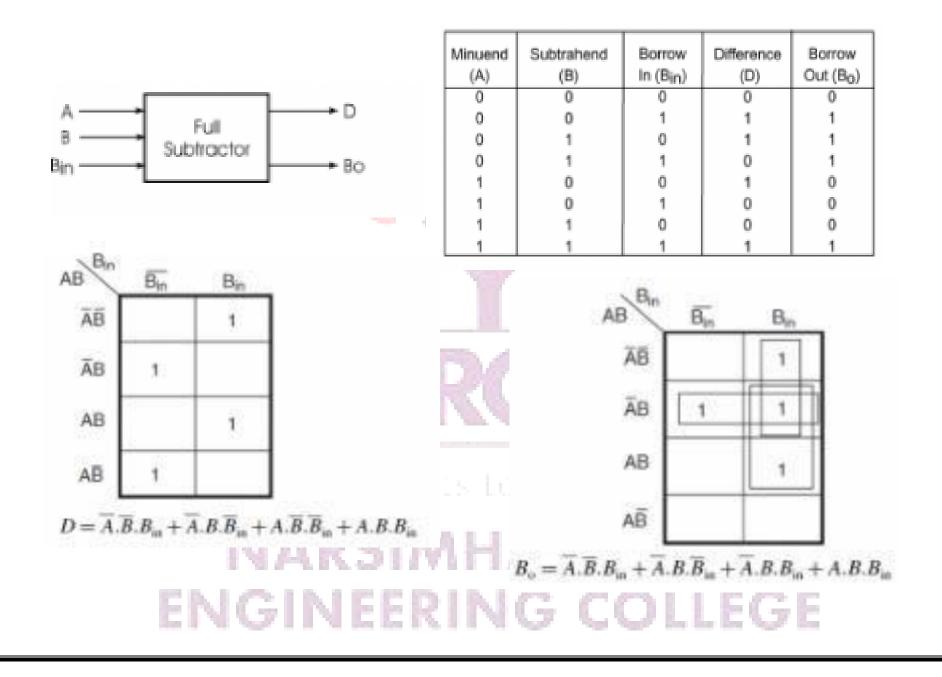

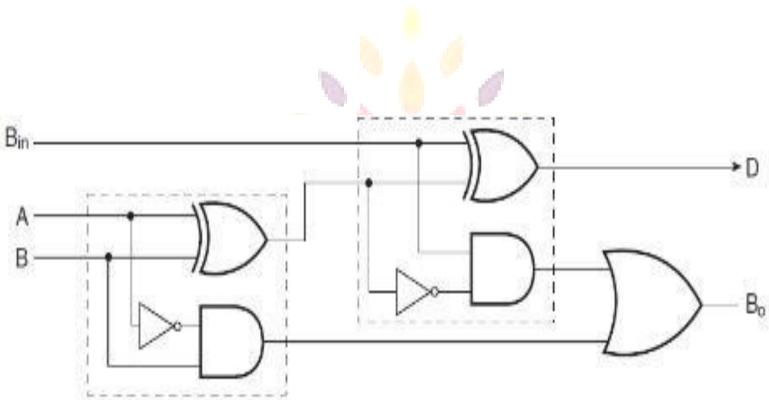

### **Full Subtractor**

# VORT TOPIS TO SUCCESS... NARSIMHA REDDY ENGINEERING COLLEGE

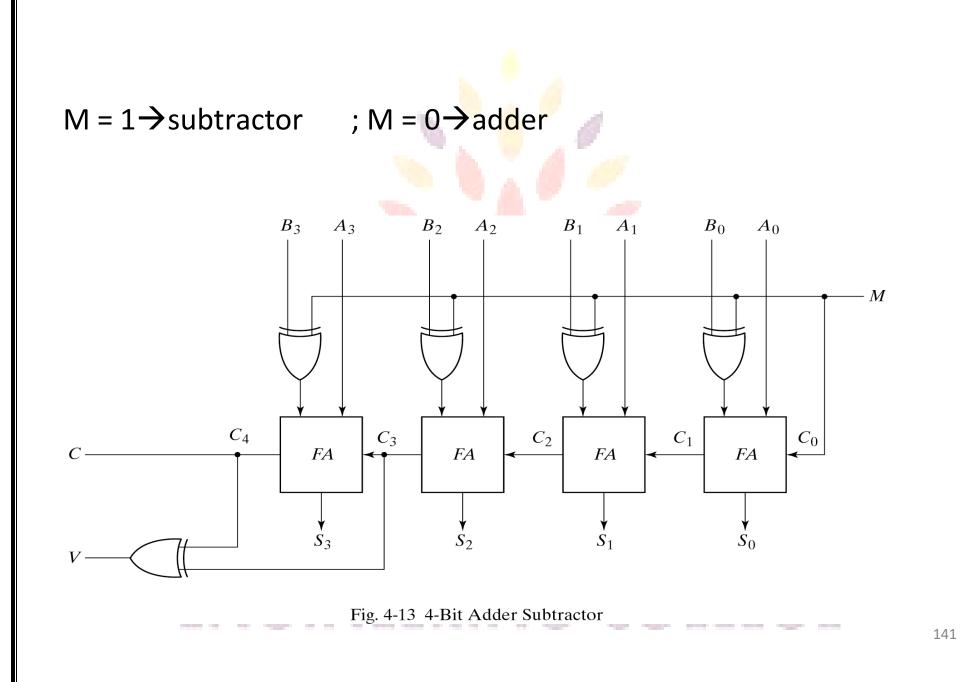

# Binary adder

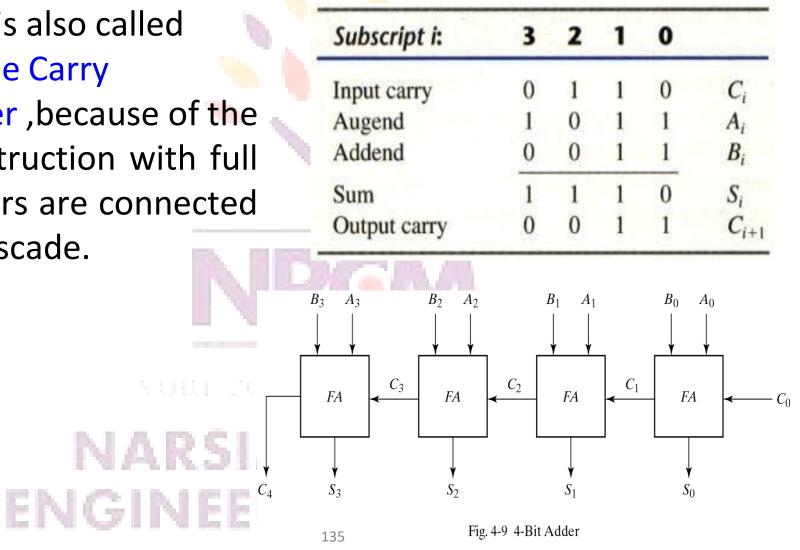

This is also called • **Ripple Carry** Adder , because of the construction with full adders are connected in cascade.

- Fig.4-9 causes a unstable factor on carry bit, and produces a longest propagation delay.

- The signal from C<sub>i</sub> to the output carry C<sub>i+1</sub>, propagates through an AND and OR gates, so, for an n-bit RCA, there are 2n gate levels for the carry to propagate from input to output.

your roots to success...

## NARSIMHA REDDY ENGINEERING COLLEGE

- Because the propagation delay will affect the output signals on different time, so the signals are given enough time to get the precise and stable outputs.

- The most widely used technique employs the principle of carry look-ahead to improve the speed of the algorithm.

Fig. 4-10 Full Adder with P and G Shown

### **Boolean functions**

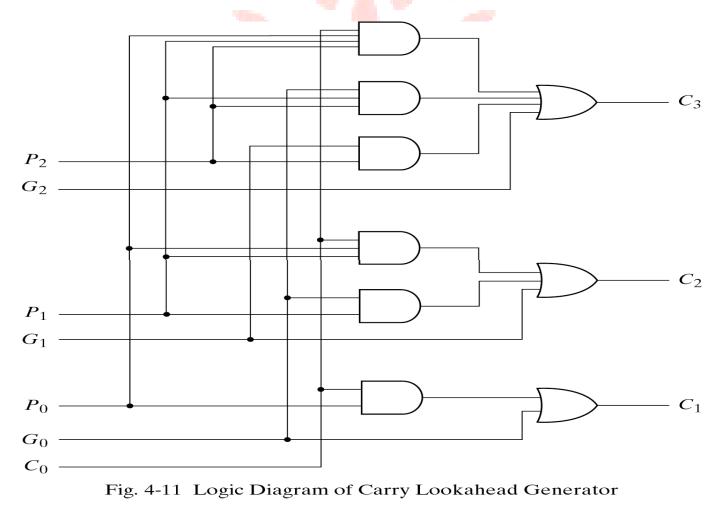

$P_i = A_i \bigoplus B_i$  steady state value  $G_i = A_i B_i$  steady state value Output sum and carry  $S_i = P_i \bigoplus C_i$  $C_{i+1} = G_i + P_i C_i$ G<sub>i</sub> : carry generate P<sub>i</sub> : carry propagate  $C_0$  = input carry  $C_1 = G_0 + P_0 C_0$  $C_2 = G_1 + P_1C_1 = G_1 + P_1G_0 + P_1P_0C_0$  $C_3 = G_2 + P_2C_2 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$

C<sub>3</sub> does not have to wait for C<sub>2</sub> and C<sub>1</sub> to propagate.

# Logic diagram of carry look-ahead generator

•  $C_3$  is propagated at the same time as  $C_2$  and  $C_1$ .

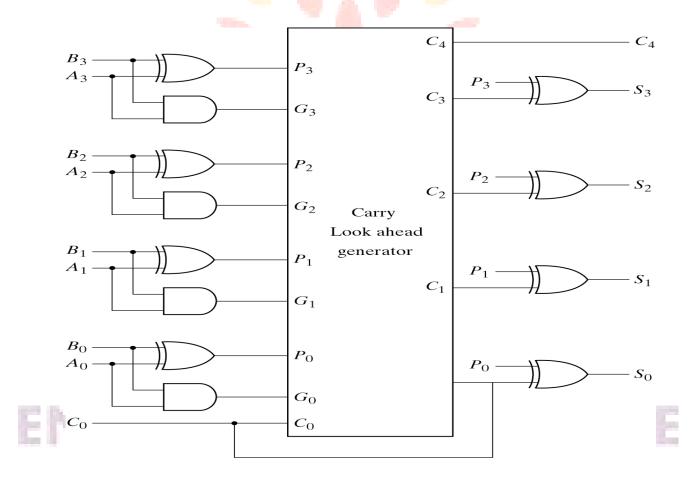

### 4-bit adder with carry lookahead

Delay time of n-bit CLAA = XOR + (AND + OR) + XOR

Fig. 4-12 4-Bit Adder with Carry Lookahead

####

🤊 🔔 🦉 🍃

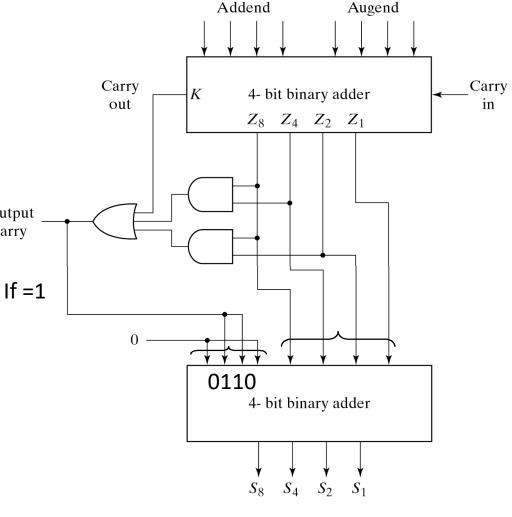

### BCD adder can't exceed 9 on each input digit. K is the carry.

100

#### Table 4-5 Derivation of BCD Adder

| Decima | BCD Sum               |    |            |                | Binary Sum |                |                |    |                |   |

|--------|-----------------------|----|------------|----------------|------------|----------------|----------------|----|----------------|---|

|        | <i>S</i> <sub>1</sub> | Sz | <b>S</b> 4 | S <sub>8</sub> | с          | Z <sub>1</sub> | Z <sub>2</sub> | Z4 | Z <sub>8</sub> | ĸ |

| 0      | 0                     | 0  | 0          | 0              | 0          | 0              | 0              | 0  | 0              | 0 |

| 1      | 1                     | 0  | 0          | 0              | 0          | 1              | 0              | 0  | 0              | 0 |

| 2      | 0                     | 1  | 0          | 0              | 0          | 0              | 1              | 0  | 0              | 0 |

| 3      | 1                     | 1  | 0          | 0              | 0          | 1              | 1              | 0  | 0              | 0 |

| 4      | 0                     | 0  | 1          | 0              | 0          | 0              | 0              | 1  | 0              | 0 |

| 5      | 1                     | 0  | 1          | 0              | 0          | 1              | 0              | 1  | 0              | 0 |

| 6      | 0                     | 1  | 1          | 0              | 0          | 0              | 1              | 1  | 0              | 0 |

| 7      | 1                     | 1  | 1          | 0              | 0          | 1              | 1              | 1  | 0              | 0 |

| 8      | 0                     | 0  | 0          | 1              | 0          | 0              | 0              | 0  | 1              | 0 |

| 9      | 1                     | 0  | 0          | 1              | 0          | 1              | 0              | O  | 1              | 0 |

| 10     | 0                     | 0  | 0          | 0              | 1          | 0              | 1              | 0  | 1              | 0 |

| 11     | 1                     | 0  | 0          | 0              | 1          | 1              | 1              | 0  | 1              | 0 |

| 12     | 0                     | 1  | 0          | 0              | 1          | 0              | 0              | 1  | 1              | 0 |

| 13     | 1                     | 1  | 0          | 0              | 1          | 1              | 0              | 1  | 1              | 0 |

| 14     | 0                     | 0  | 1          | 0              | 1          | 0              | 1              | 1  | 1              | 0 |

| 15     | 1                     | 0  | 1          | 0              | 1          | 1              | 1              | 1  | 1              | 0 |

| 16     | 0                     | 1  | 1          | 0              | 1          | 0              | 0              | 0  | 0              | 1 |

| 17     | 1                     | 1  | 1          | 0              | 1          | 1              | 0              | 0  | 0              | 1 |

| 18     | 0                     | 0  | 0          | 1              | 1          | 0              | 1              | 0  | 0              | 1 |

| 19     | 1                     | 0  | 0          | 1              | 1          | 1              | 1              | 0  | 0              | 1 |

# Rules of BCD adder

- When the binary sum is greater than 1001, we obtain a non-valid BCD representation.

- The addition of binary 6(0110) to the binary sum converts it to the correct BCD representation and also produces an output carry as required.

- To distinguish them from binary 1000 and 1001, which also have a 1 in position Z<sub>8</sub>, we specify further that either Z<sub>4</sub> or Z<sub>2</sub> must have a 1.

# NAR=K+Z8Z4+Z8Z2 REDDY ENGINEERING COLLEGE

# Implementation of BCD adder

- A decimal parallel adder that adds n decimal digits needs n

BCD adder stages.

Fig. 4-14 Block Diagram of a BCD Adder

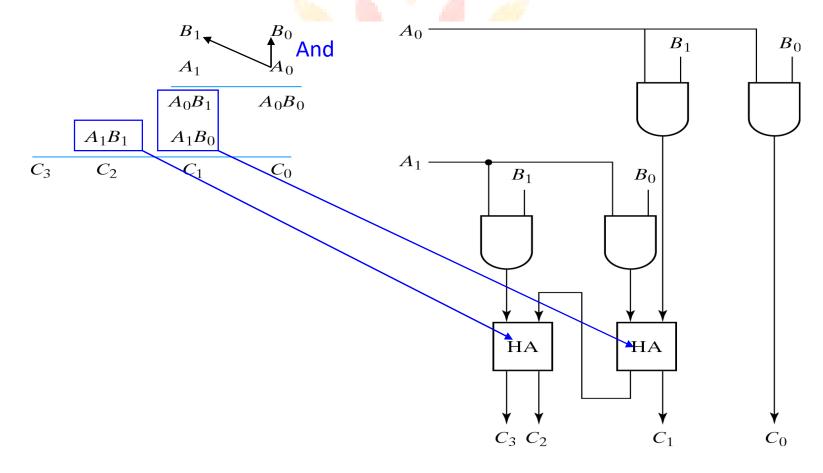

# 4-6. Binary multiplier

Usually there are more bits in the partial products and it is necessary to use full adders to produce the sum of the partial products.

Fig. 4-15 2-Bit by 2-Bit Binary Multiplier

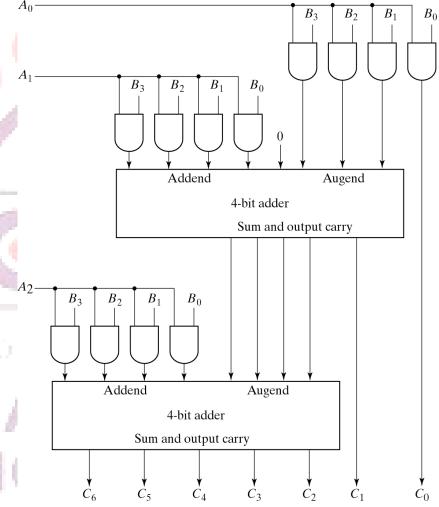

## 4-bit by 3-bit binary multiplier

- For J multiplier bits and K multiplicand bits we need (J X K) AND gates and (J – 1) Kbit adders to produce a product of J+K bits.

- K=4 and J=3, we need 12

AND gates and two 4-bit

adders.

ENGINEERING

Fig. 4-16 4-Bit by 3-Bit Binary Multiplier

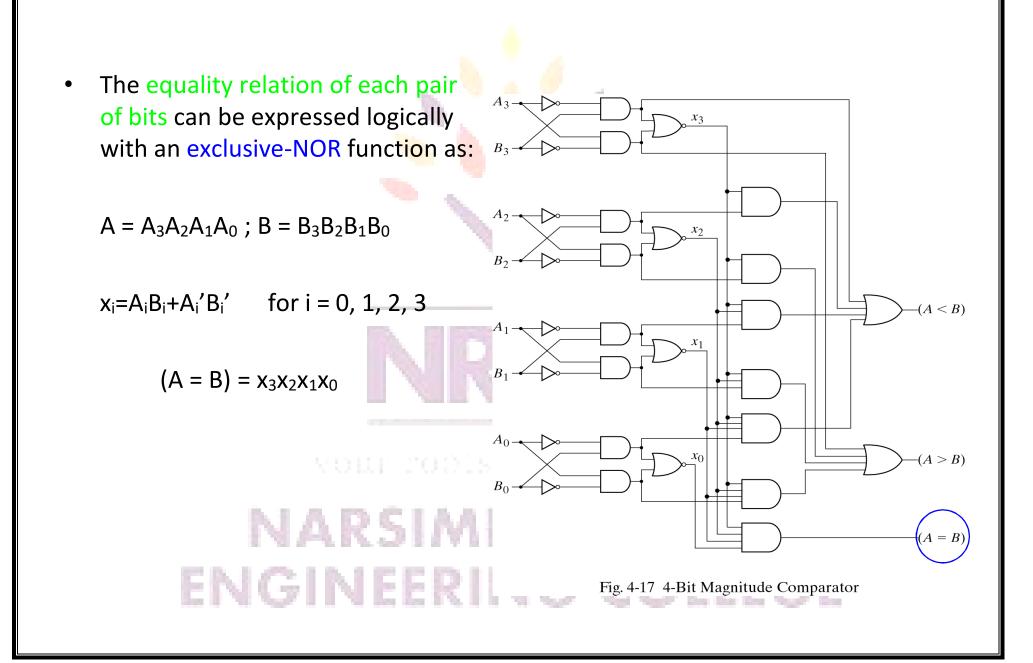

- We inspect the relative magnitudes of pairs of MSB. If equal, we compare the next lower significant pair of digits until a pair of unequal digits is reached.

- If the corresponding digit of A is 1 and that of B is 0, we conclude that A>B.

(A > B) =  $A_{3}B'_{3} + x_{3}A_{2}B'_{2} + x_{3}x_{2}A_{1}B'_{1} + x_{3}x_{2}x_{1}A_{0}B'_{0}$  (A < B) =  $A'_{3}B_{3} + x_{3}A'_{2}B_{2} + x_{3}x_{2}A'_{1}B_{1} + x_{3}x_{2}x_{1}A'_{0}B_{0}$

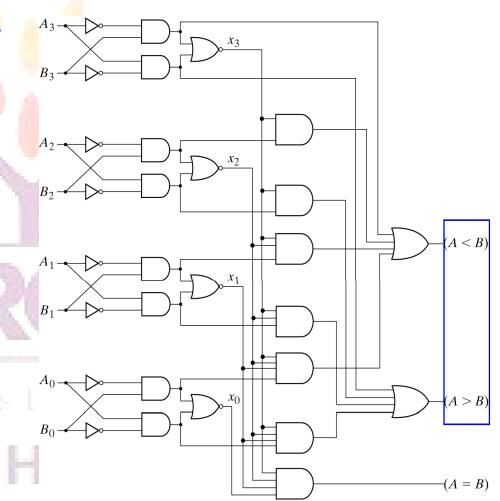

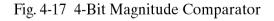

- The decoder is called n-to-m-line decoder, where m≤2<sup>n</sup>.

- the decoder is also used in conjunction with other code converters such as a BCD-to-seven\_segment decoder.

- 3-to-8 line decoder: For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1.

ENGINEERING COLLEGE

### Implementation and truth table

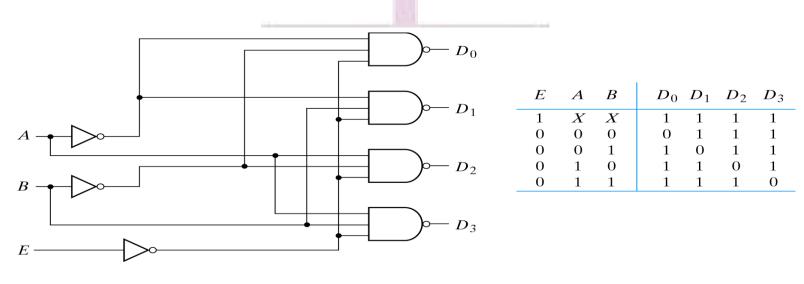

## Decoder with enable input

- Some decoders are constructed with NAND gates, it becomes more economical to generate the decoder minterms in their complemented form.

- As indicated by the truth table , only one output can be equal to 0 at any given time, all other outputs are equal to 1.

(a) Logic diagram

(b) Truth table

Fig. 4-19 2-to-4-Line Decoder with Enable Input

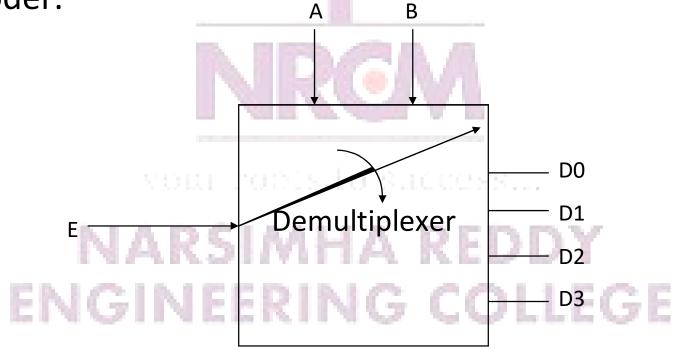

# Demultiplexer

- A decoder with an enable input is referred to as a decoder/demultiplexer.

- The truth table of demultiplexer is the same with decoder.

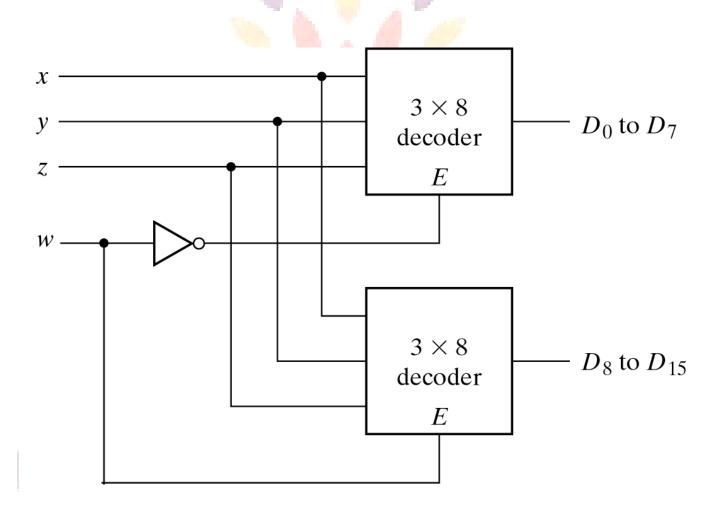

# 3-to-8 decoder with enable implement the 4-to-16 decoder

Fig. 4-20 4  $\times$  16 Decoder Constructed with Two 3  $\times$  8 Decoders 153

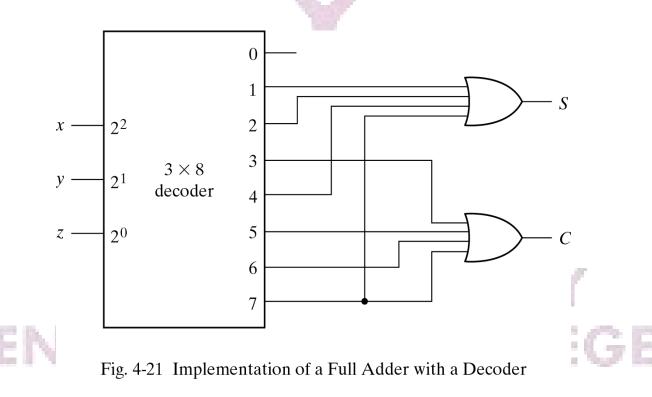

# Implementation of a Full Adder with a Decoder

From table 4-4, we obtain the functions for the combinational circuit in sum of minterms:

> $S(x, y, z) = \sum (1, 2, 4, 7)$ C(x, y, z) =  $\sum (3, 5, 6, 7)$

####

- An encoder is the inverse operation of a decoder.

- We can derive the Boolean functions by table 4-7

$z = D_1 + D_3 + D_5 + D_7$   $y = D_2 + D_3 + D_6 + D_7$  $x = D_4 + D_5 + D_6 + D_7$

| Inputs |       |       |       |       |       |       |    | Outputs |   |   |

|--------|-------|-------|-------|-------|-------|-------|----|---------|---|---|

| $D_0$  | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $D_6$ | D7 | x       | У | z |

| 1      | 0     | 0     | 0     | 0     | 0     | 0     | 0  | 0       | 0 | 0 |

| 0      | 1     | 0     | 0     | 0     | 0     | 0     | 0  | 0       | 0 | 1 |

| 0      | 0     | 1     | 0     | 0     | 0     | 0     | 0  | 0       | 1 | C |

| 0      | 0     | 0     | 1     | 0     | 0     | 0     | 0  | 0       | 1 | 1 |

| 0      | 0     | 0     | 0     | 1     | 0     | 0     | 0  | 1       | 0 | C |

| 0      | 0     | 0     | 0     | 0     | 1     | 0     | 0  | 1       | 0 | 1 |

| 0      | 0     | 0     | 0     | 0     | 0     | 1     | 0  | 1       | 1 | C |

| 0      | 0     | 0     | 0     | 0     | 0     | 0     | 1  | 1       | 1 | 1 |

#### Table 4-7 Truth Table of Octal-to-Binary Encoder

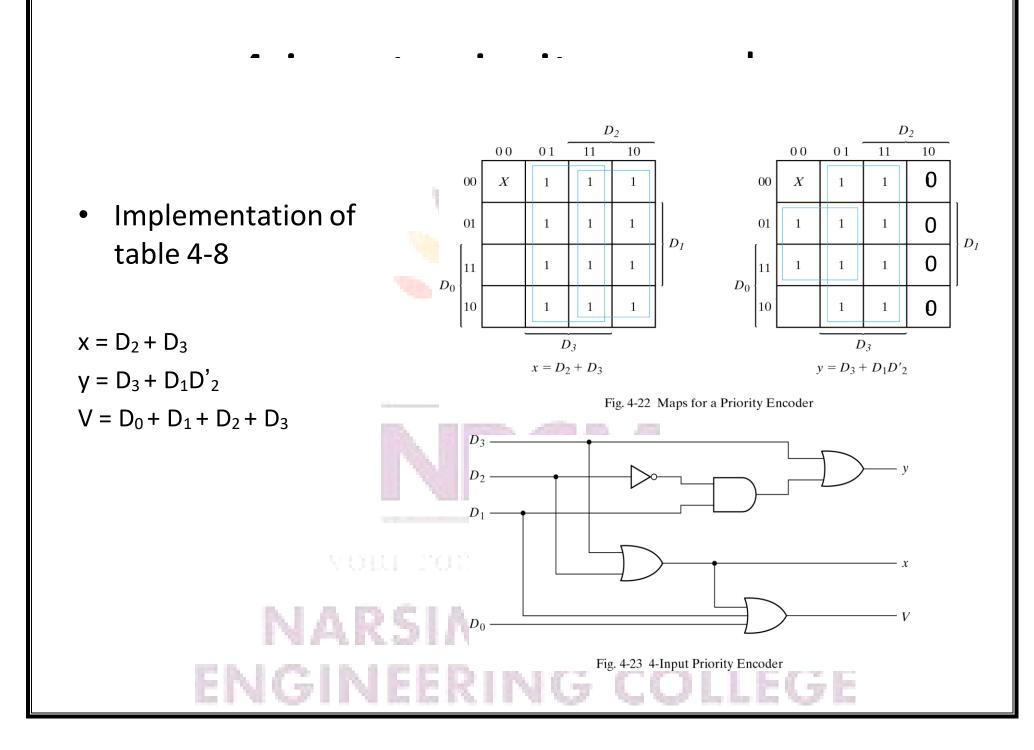

#### If two inputs are active simultaneously, the output produces an undefined combination. We can establish an input priority to ensure that only one input is encoded.

- Another ambiguity in the octal-to-binary encoder is that an output with all 0's is generated when all the inputs are 0; the output is the same as when D<sub>0</sub> is equal to 1.

- The discrepancy tables on Table 4-7 and Table 4-8 can resolve aforesaid condition by providing one more output to indicate that at least one input is equal to 1.

# NARSIMHA REDDY ENGINEERING COLLEGE <sup>156</sup>

| V=1→valid inputs                | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. | Table 4-8         Truth Table of a Priority Encoder |      |                |   |        |   |  |  |

|---------------------------------|------------------------------------------|-----------------------------------------------------|------|----------------|---|--------|---|--|--|

| X's in output columns represent |                                          | Inp                                                 | outs |                | ( | Dutput | s |  |  |

| don't-care conditions           | Do                                       | D1                                                  | D2   | D <sub>3</sub> | x | y      | V |  |  |

| X's in the input columns are    | 0                                        | 0                                                   | 0    | 0              | X | X      | 0 |  |  |

| useful for representing a truth | 1                                        | 0                                                   | 0    | 0              | 0 | 0      | 1 |  |  |

|                                 | X                                        | 1                                                   | 0    | 0              | 0 | 1      | 1 |  |  |

| table in condensed form.        | X                                        | X                                                   | 1    | 0              | 1 | 0      | 1 |  |  |

| Instead of listing all 16       | X                                        | X                                                   | X    | 1              | 1 | 1      | 1 |  |  |

# NARSIMHA REDDY ENGINEERING COLLEGE

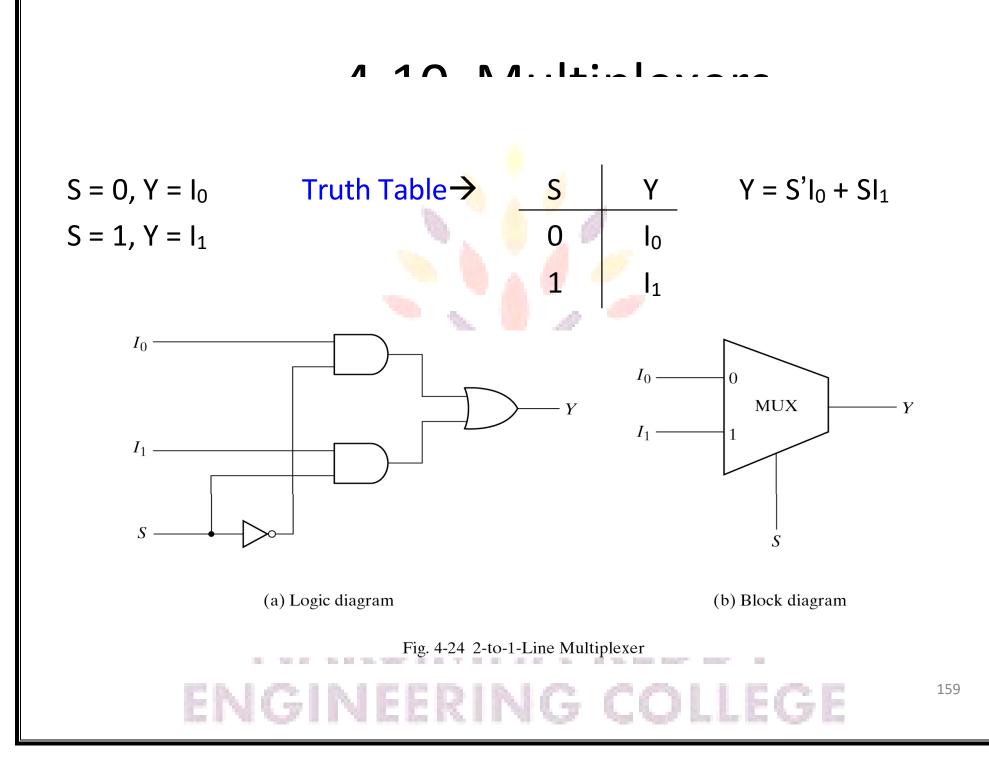

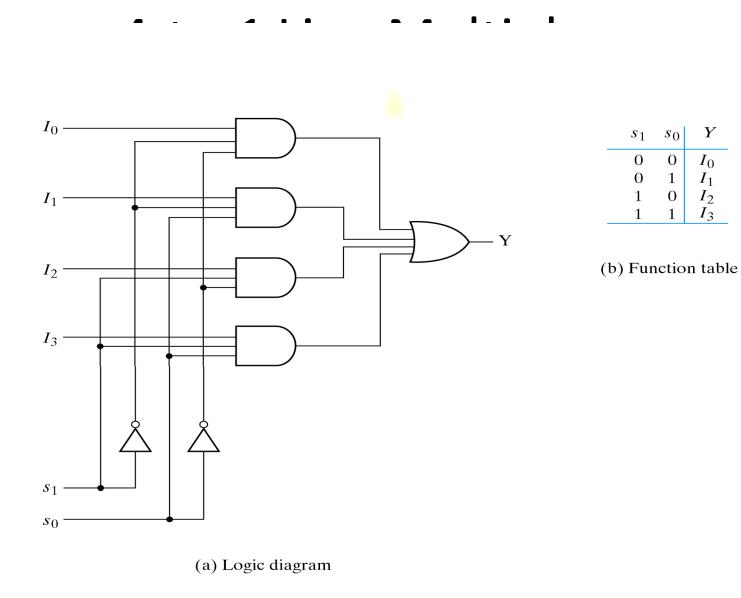

Fig. 4-25 4-to-1-Line Multiplexer

ENGINEERING COLLEGE

160

Y

$I_0

I_1

I_2

I_3$

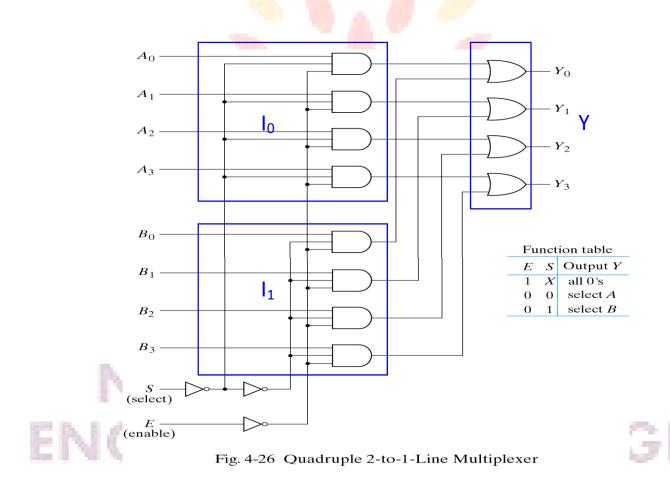

Multiplexer circuits can be combined with common selection inputs to provide multiple-bit selection logic. Compare with Fig4-24.

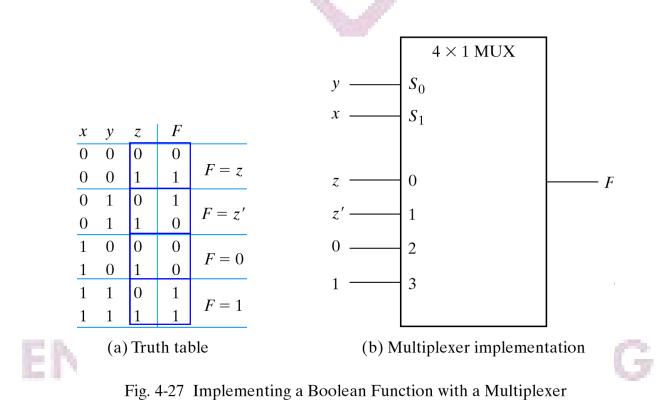

A more efficient method for implementing a Boolean function of n variables with a multiplexer that has n-1 selection inputs.

$$F(x, y, z) = \Sigma(1, 2, 6, 7)$$

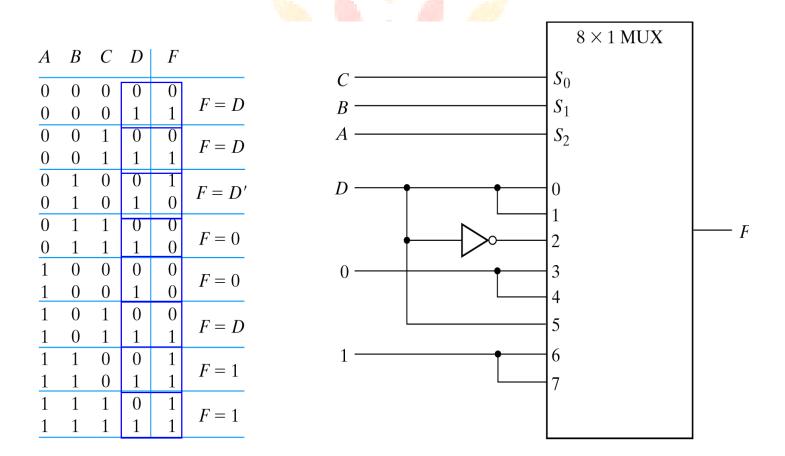

#### $F(A, B, C, D) = \Sigma(1, 3, 4, 11, 12, 13, 14, 15)$

Fig. 4-28 Implementing a 4-Input Function with a Multiplexer

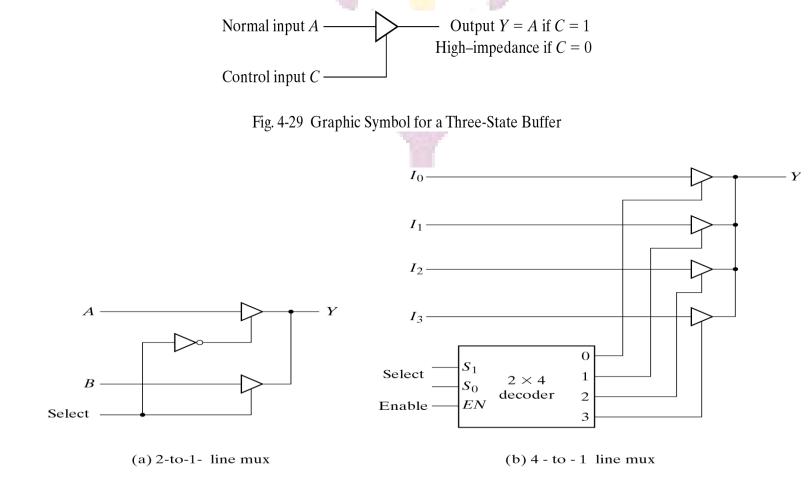

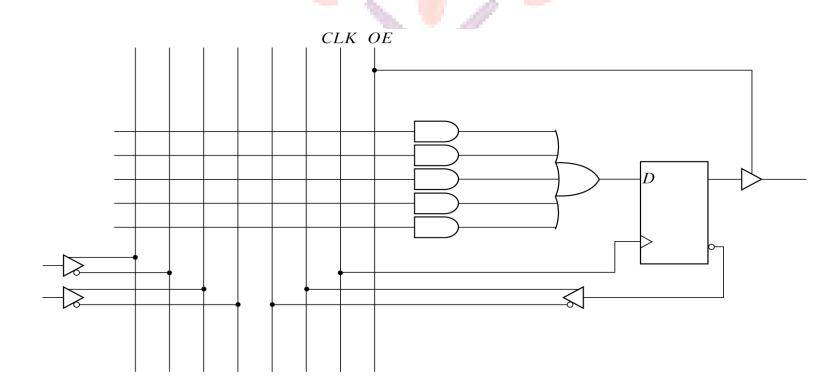

### Three-State Gates

A multiplexer can be constructed with three-state gates.

Fig. 4-30 Multiplexers with Three-State Gates

#### Sequential Circuits

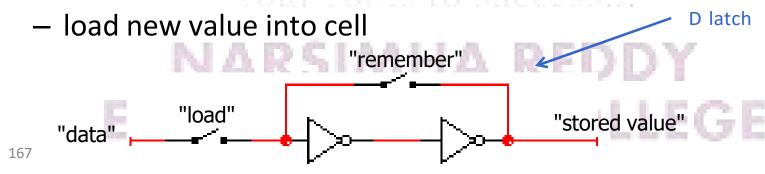

- A sequential circuit is one whose outputs depend not only on its current inputs, but also on the past sequence of inputs.

- In other words, sequential circuits must be able to "remember" (i.e., store) the past history of the inputs in order to produce the present output.

- The information about the previous inputs history is called the state of the system.

- A circuit that uses n binary state variables to store its past history can take up to 2<sup>n</sup> different states.

- Since n is always finite, sequential circuits are also called finite state machines (FSM).